# TM 990

# TM 990/189 Microcomputer User's Guide

MICROPROCESSOR SERIES

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

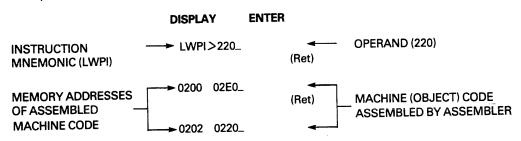

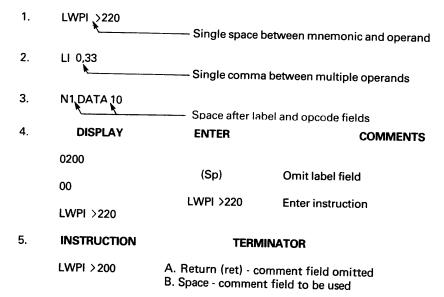

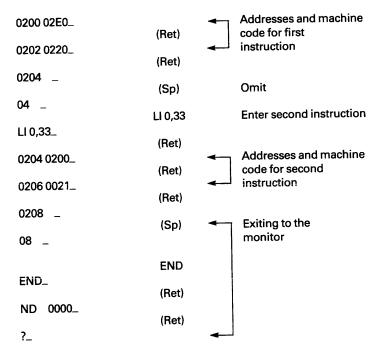

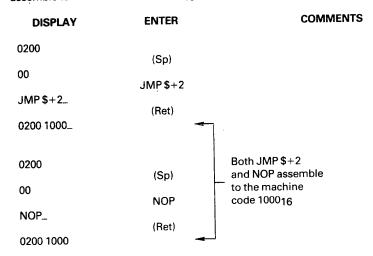

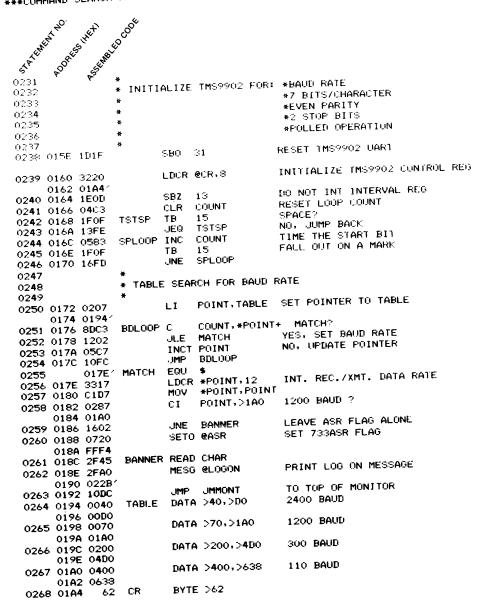

Copyright © 1979

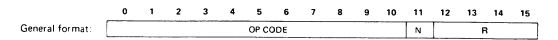

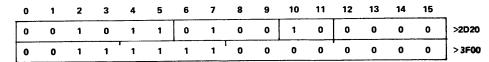

Texas Instruments Incorporated

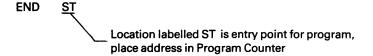

# **TABLE OF CONTENTS**

| Section                                                                                                                                  | Title                                                                                                                                                                                                                                                                                                  | Page                                                                             |

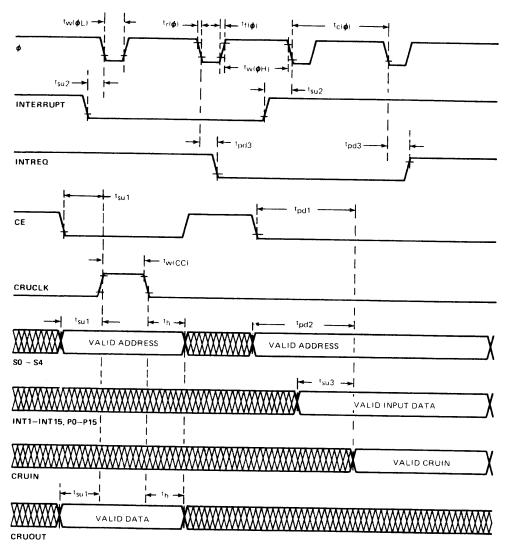

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                                          | I. INTRODUCTION                                                                                                                                                                                                                                                                                        |                                                                                  |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                                          | General Manual Organization General Specifications Glossary Applicable Documents                                                                                                                                                                                                                       | 1-4                                                                              |

|                                                                                                                                          | II. INSTALLATION AND OPERATION                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.3.1<br>2.5.3.2<br>2.5.3.3<br>2.5.3.4<br>2.5.3.5<br>2.6<br>2.7<br>2.7.1 | General Required Equipment Power Up Procedure Operation Keyboard Keyboard Description Keyboard Use Special Keys Description Shift Display Left (←D) Display Right (→D) External Terminal Use LOAD Switch L.E.D. Display Using Audio Cassette Interface (ACI) Recorder Considerations Example Operation | 2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-5<br>2-5<br>2-5<br>2-5<br>2-5<br>2-6<br>2-8 |

|                                                                                                                                          | III. UNIBUG MONITOR                                                                                                                                                                                                                                                                                    |                                                                                  |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8                                                | General UNIBUG Commands Program Example Typewriter Program (T) Memory Inspect/Change (M) Assembler Execute (A) Assembler Execute with Current Symbol Table (B) CRU Inspect/Change (C) Dump Memory to Cassette (D) Execute to Breakpoint (E) Status Register (F) Inspect/Change                         | 3-1<br>3-2<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-8<br>3-9                      |

| 3.3.9<br>3.3.10<br>3.3.11<br>3.3.12<br>3.3.13<br>3.3.14<br>3.3.15                                                                        | Jump to Start of Expansion EPROM (J)  Load Memory From Cassette (L)  Program Counter (P) Inspect/Change  Workspace Register Inspect/Change (R)  Single Step(s)  Workspace Pointer Inspect/Change (W)  New Line Request (RET)                                                                           | 3-10<br>3-11<br>3-12<br>3-13<br>3-13                                             |

| 3,3,16<br>3,4<br>3,4,1                                                                                                                   | Terminal Load/Dump Option (\$)  User Accessible Utilities  Write One Hexadecimal Character to Terminal (XOP 8)*                                                                                                                                                                                        | 3-14                                                                             |

# **TABLE OF CONTENTS (Continued)**

| Section                                                                                                                                                                                        | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.5                                                                                                                                      | Read Hexadecimal Word From Terminal (XOP 9) Write Four Hexadecimal Characters to Terminal (XOP 10)* Echo Character (XOP 11) Write One Character to Terminal (XOP 12)* Read One Character From Terminal (XOP 13) Write Message to Terminal (XOP 14) UNIBUG Error Message                                                                                                                                                                                                       | 3-17<br>3-18<br>3-18<br>3-18<br>3-19                                                                                                                  |

|                                                                                                                                                                                                | IV. SYMBOLIC ASSEMBLER                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                       |

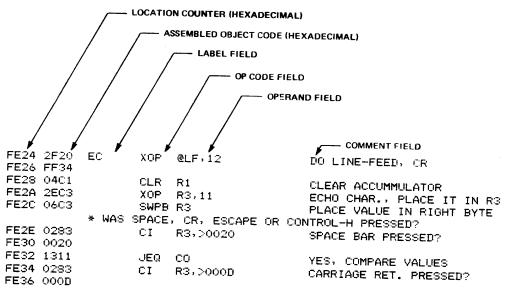

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br>4.5<br>4.6<br>4.7<br>4.8<br>4.8.1.1<br>4.8.1.2<br>4.8.1.3<br>4.8.1.4<br>4.8.1.5<br>4.8.1.6 | General Labels and Comments Labels Comments Use Dollar Sign to Indicate "At This Location" Expressions Cancel Source Statement Being Input Translate Characters Into ASCII Code Using Single Quotes Assembler Action Operation Calling the Assembler Exiting to the Monitor Entering Instructions Errors Pseudo-Instruction TM 990/189 Symbolic Assembler Listing Listing Format Location Counter Assembled Object Code Label Field Op Code Field Operand Field Comment Field | . 4-1<br>. 4-1<br>. 4-1<br>. 4-2<br>. 4-2<br>. 4-2<br>. 4-2<br>. 4-3<br>. 4-3<br>. 4-3<br>. 4-3<br>. 4-7<br>. 4-7<br>. 4-7<br>. 4-7<br>. 4-8<br>. 4-8 |

|                                                                                                                                                                                                | V. INSTRUCTION SET FOR THE TM 990/189                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

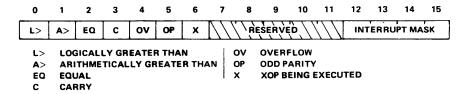

| 5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.3.1<br>5.3.3.2<br>5.3.3.3<br>5.3.3.4<br>5.3.3.5<br>5.3.3.6<br>5.3.3.7<br>5.3.3.8                                                           | General User Memory Hardware Registers Program Counter (PC) Workspace Pointer (WP) Status Register (ST) Logical Greater Than Arithmetic Greater Than Equal Carry Overflow Odd Parity Extended Operation Status Bit Summary                                                                                                                                                                                                                                                    | 5-1<br>5-2<br>5-2<br>5-4<br>5-4<br>5-4<br>5-4<br>5-5<br>5-5                                                                                           |

# **TABLE OF CONTENTS (Continued)**

| Section                                                                                                                                                                                                 | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

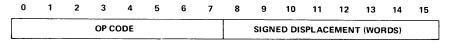

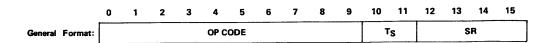

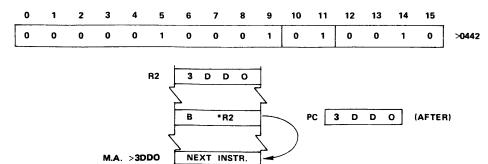

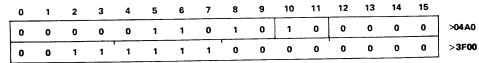

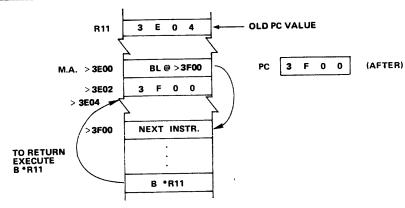

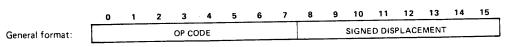

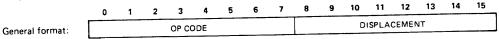

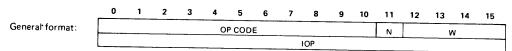

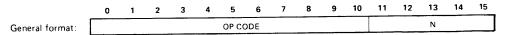

| 5.4<br>5.5<br>5.5.1<br>5.5.1.2<br>5.5.1.3<br>5.5.1.4<br>5.5.1.6<br>5.5.1.7<br>5.6.1<br>5.6.2<br>5.6.2<br>5.6.2.1<br>5.6.2.2<br>5.6.3<br>5.6.4<br>5.6.5<br>5.6.6<br>5.6.7<br>5.6.8<br>5.6.8.1<br>5.6.8.2 | Instruction Formats and Addressing Modes Addressing Modes Direct Register Addressing (T = 002) Indirect Register Addressing (T = 012) Indirect Register Autoincrement Addressing (T = 112) Symbolic Memory Addressing, Not Indexed (T = 102) Symbolic Memory Addressing, Indexed (T = 102) Immediate Addressing Program Counter Relative Addressing Instructions Format 1 Instructions Format 2 Instructions Jump Instructions CRU Single-Bit Instructions Format 4 (CRU Multibit) Instructions Format 5 (Shift) Instructions Format 7 (RTWP, Control) Instructions Format 8 (Immediate, Internal Register Load/Store) Instructions Internal Register Load Immediate Instructions Internal Register Store Instructions Internal Register Store Instructions | 5-17<br>5-12<br>5-12<br>5-14<br>5-15<br>5-17<br>5-18<br>5-18<br>5-22<br>5-24<br>5-26<br>5-26<br>5-26<br>5-30<br>5-31<br>5-34<br>5-36<br>5-36<br>5-36 |

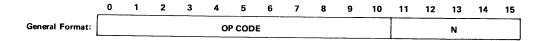

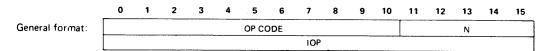

| 5.6.8.3<br>5.6.9                                                                                                                                                                                        | Format 9 (XOP) Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 5-38                                                                                                                                               |

|                                                                                                                                                                                                         | VI. ASSEMBLER DIRECTIVES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6                                                                                                                                        | General Directive Formats AORG Directive BSS Directive Data Directive End Directive EQU Directive Text Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-1<br>6-2<br>6-2<br>6-2                                                                                                                             |

|                                                                                                                                                                                                         | VII. I/O PROGRAMMING USING THE CRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3<br>7.4<br>7.5                                                                                                                                              | General CRU Addressing CRU Bit Address CRU Hardware Base Address CRU Software Base Address CRU Timing CRU Instructions I/O Programming with the TMS 9901                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-3<br>7-3<br>7-3<br>7-4                                                                                                                             |

|                                                                                                                                                                                                         | VIII. THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                      |

| 8.1<br>8.1.1<br>8.2                                                                                                                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      |

٧

# TABLE OF CONTENTS (Concluded)

| Section      | Title                                            | Page   |

|--------------|--------------------------------------------------|--------|

| 8.2.1        | Data Bus                                         | 8-1    |

| 8.2.2        | Address Bus                                      | 8-3    |

| 8.2.3        | CRU Bus                                          | 8-3    |

| 8.2.4        | Control Bus                                      | 8-3    |

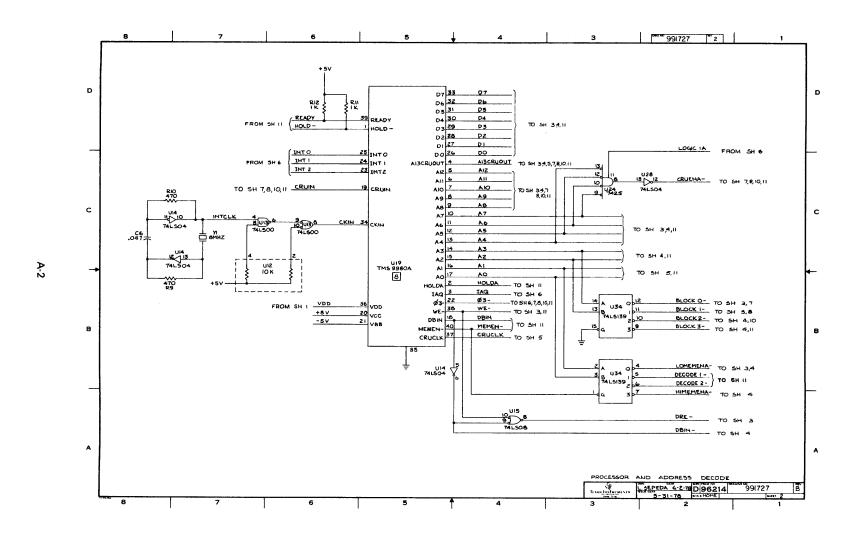

| 8.3          | Processor                                        | 8-4    |

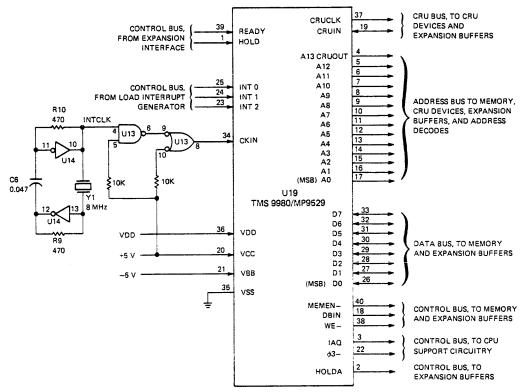

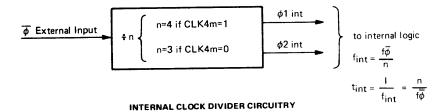

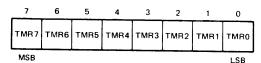

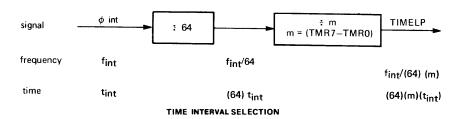

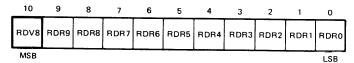

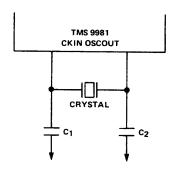

| 8.3.1        | Clock Oscillator                                 | 8-4    |

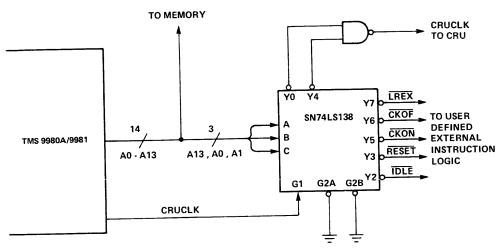

| 8.3.2        | External Instruction Decoding                    | 8-4    |

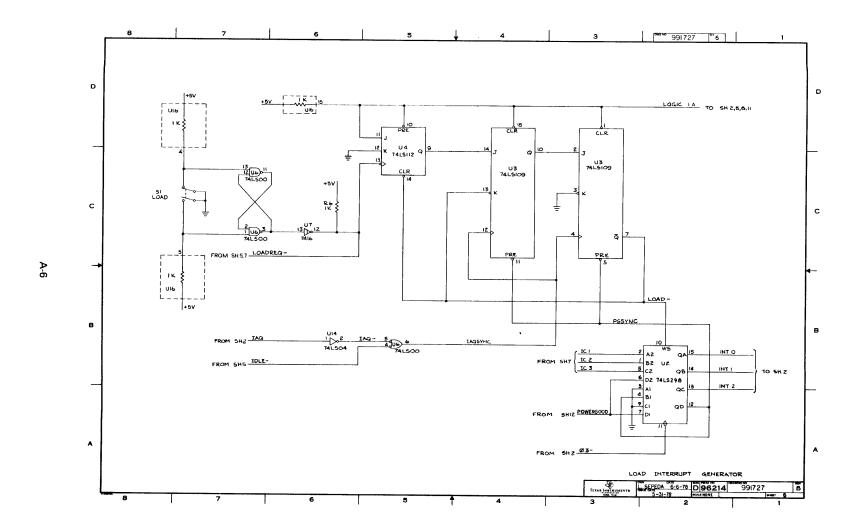

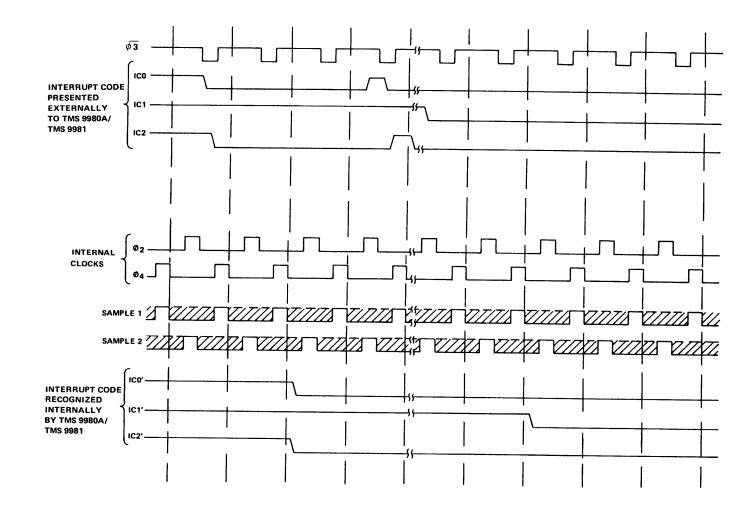

| 8.4          | Interrupts                                       | 8-8    |

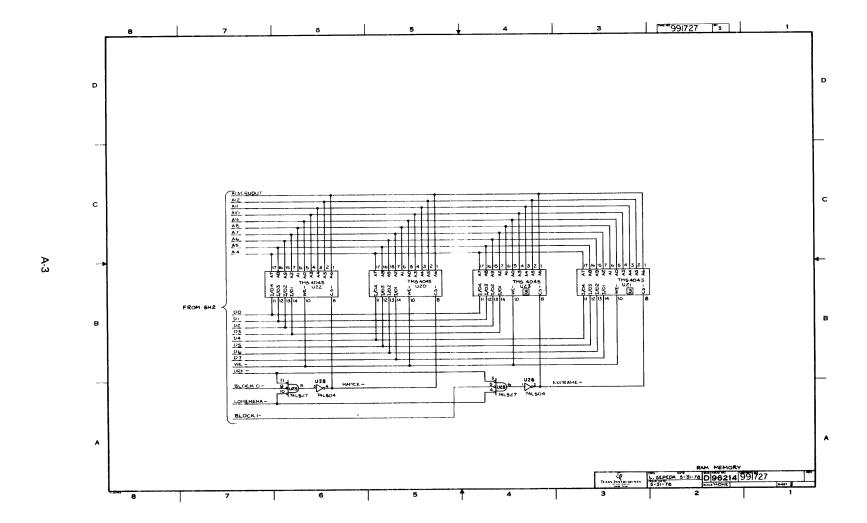

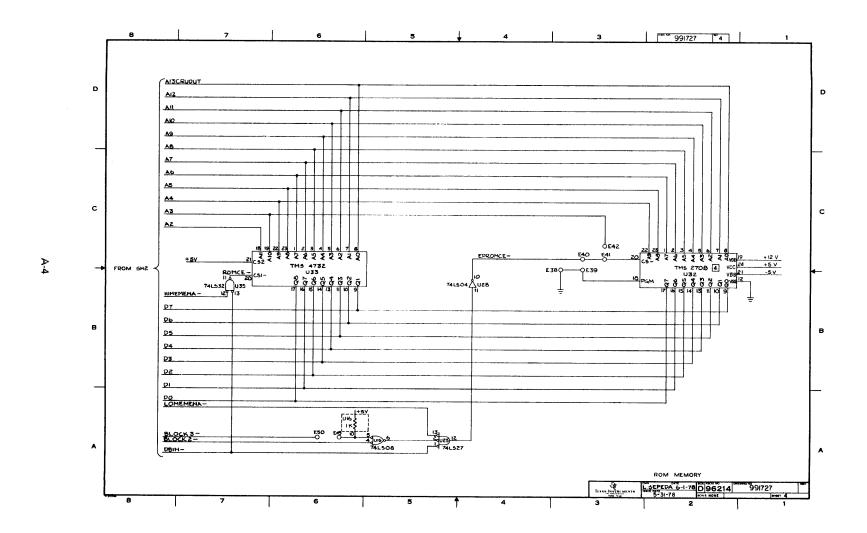

| 8.5          | Memory                                           | . 8-14 |

| 8.5.1        | Memory Address Decoding                          | . 8-14 |

| 8.5.2        | Memory Expansion                                 | . 8-14 |

| 8.6          | Input-Output                                     | . 8-18 |

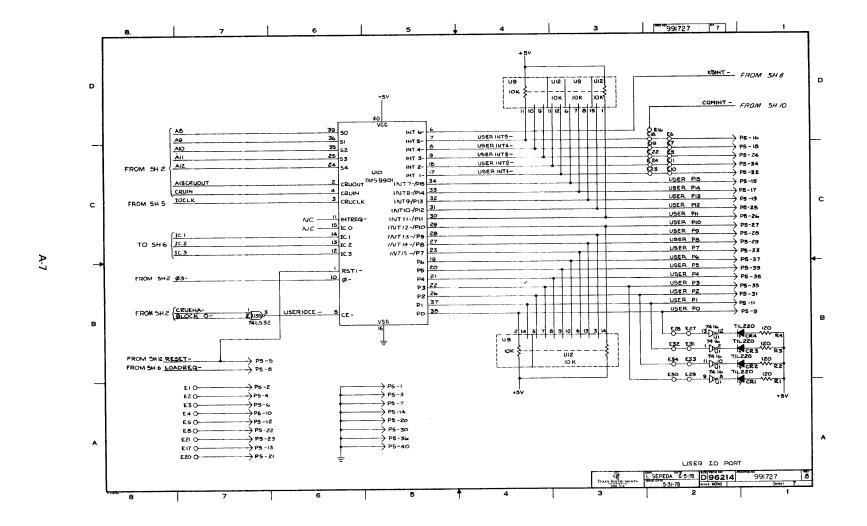

| 8.6.1        | User I/O Port                                    |        |

| 8.6.2        | System I/O Port                                  | . 8-20 |

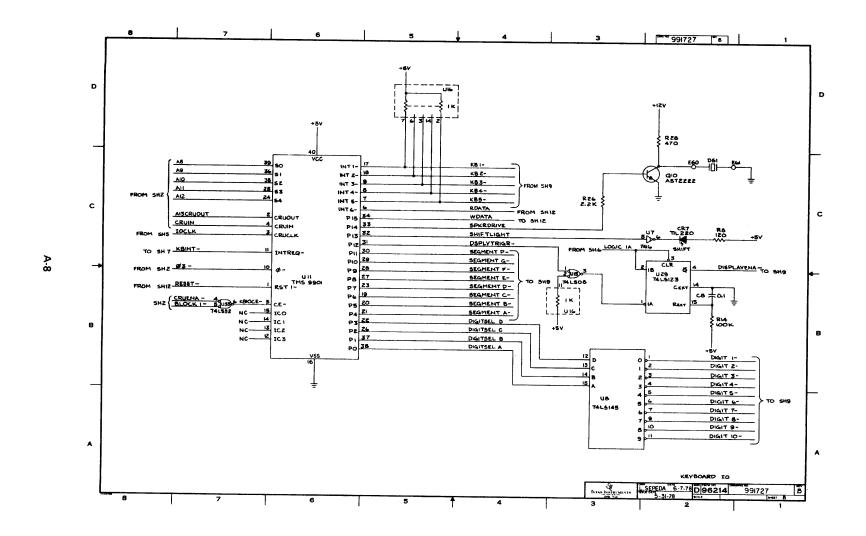

| 8.6.2.1      | Keyboard and Display Interface                   | . 8-20 |

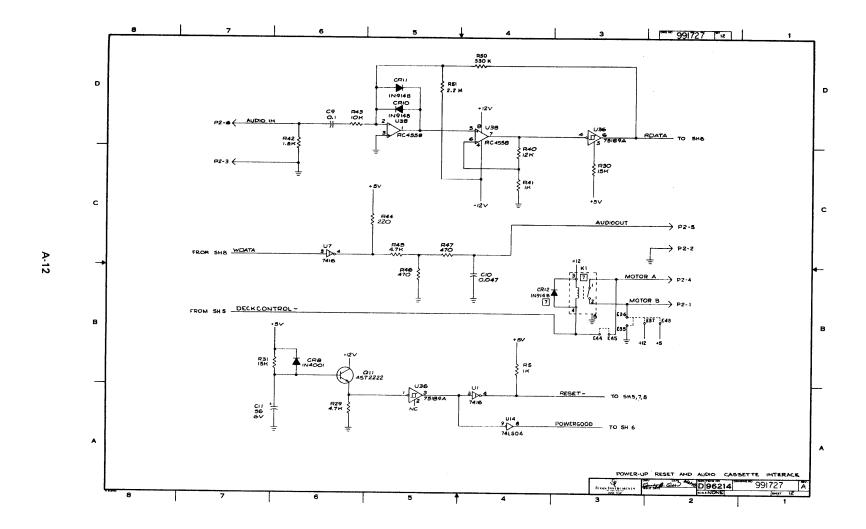

| 8.6.2.2      | Audio Cassette Interface                         | . 8-25 |

| 8.6.2.3      | Sound Disc                                       | . 8-26 |

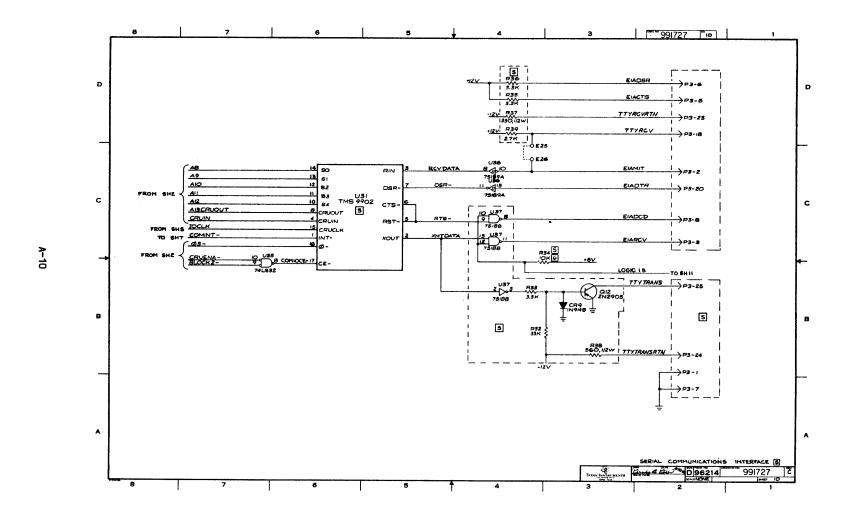

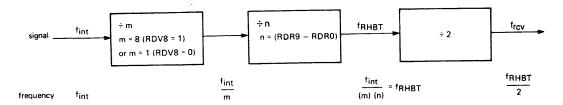

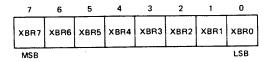

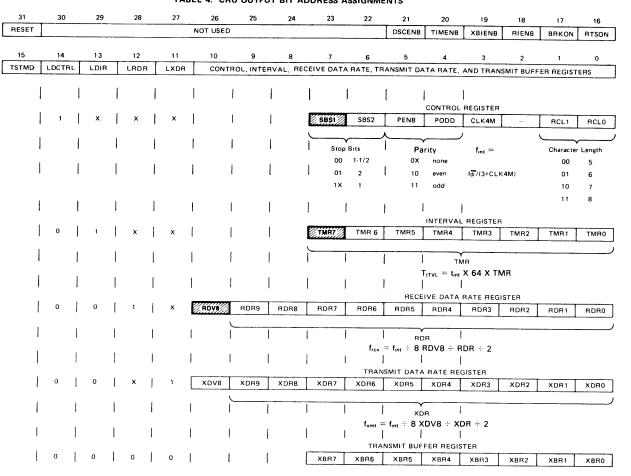

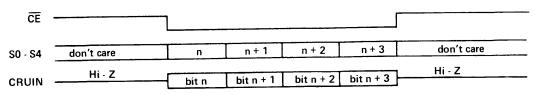

| 8.6.3        | Serial Communications Port                       | . 8-26 |

| 8.6.4        | External I/O Port                                | . 8-27 |

|              | IX. USER OPTIONS                                 |        |

| 9.1          | Introduction                                     |        |

| 9.2          | Memory Options                                   |        |

| 9.2.1        | On-Board RAM Expansion                           |        |

| 9.2.2        | On-Board EPROM, 1K Bytes                         |        |

| 9.2.3        | On-Board EPROM, 2K Bytes                         |        |

| 9.2.4        | On-Board EPROM, 4K Bytes                         |        |

| 9.2.5        | Off-Board Memory Expansion                       |        |

| 9.3          | Input-Output Options                             |        |

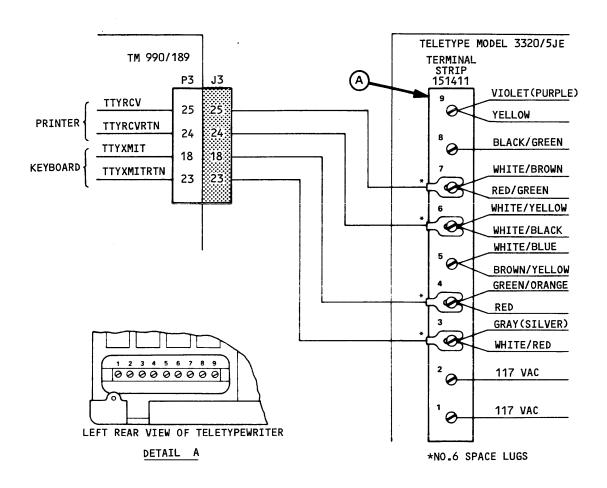

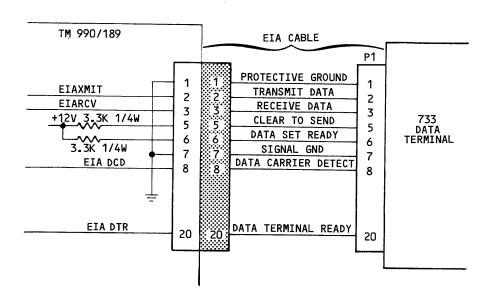

| 9.3.1        | Asynchronous Communications, EIA                 |        |

| 9.3.2        | Asynchronous Communications, TTY                 |        |

| 9.3.3        | On-Board Cassette Relay                          |        |

| 9.3.4        | Off-Board Cassette Relay                         |        |

| 9.3.5        | Off-Board CRU Expansion                          | . 9-4  |

| 9.3.6<br>9.4 | On-Board LED Disconnection                       |        |

| 9.4.1        |                                                  | 9-6    |

| 9.4.2        | Communications Interrupts System Clock Frequency | 9-6    |

| 3.4.2        | System Clock Frequency                           | 9-6    |

|              | X. TROUBLESHOOTING SUGGESTIONS                   |        |

| 10.1         | Introduction                                     | 10-1   |

| 10.2         | Troubleshooting Procedure                        |        |

| 10.2.1       | Visual Checks                                    | 10-1   |

| 10.2.2       | Static Checks                                    | 10-1   |

| 10.2.3       | Dynamic Checks                                   |        |

# APPENDICES

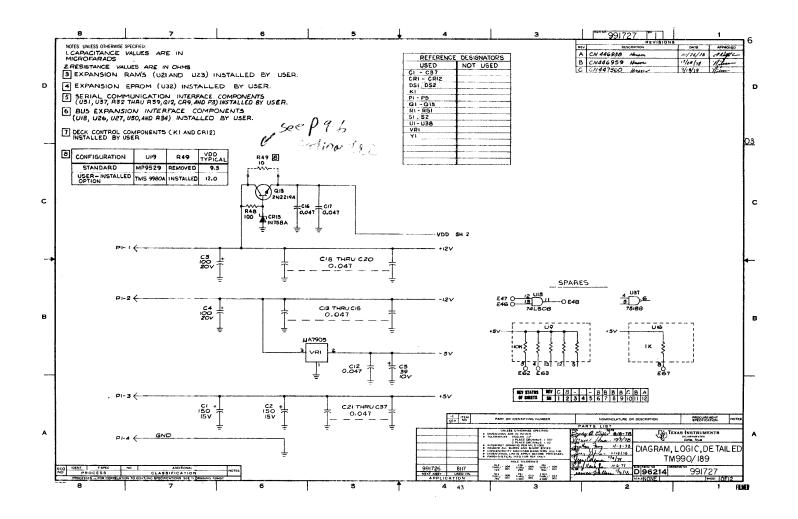

| Α | SCHEMATICS                                                  |

|---|-------------------------------------------------------------|

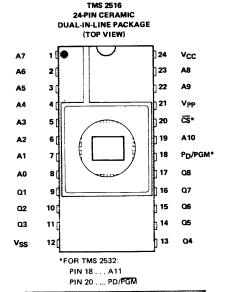

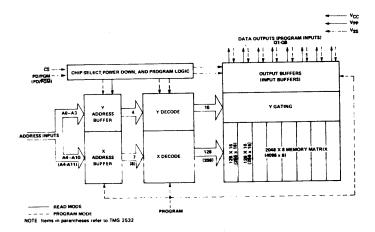

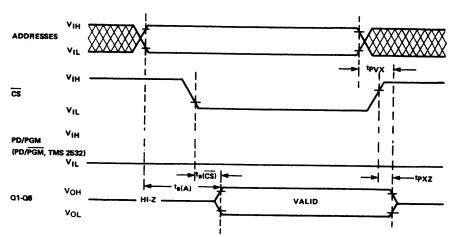

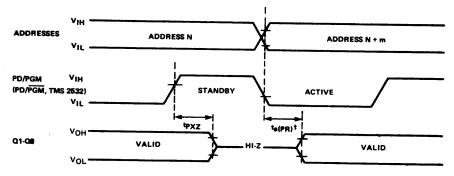

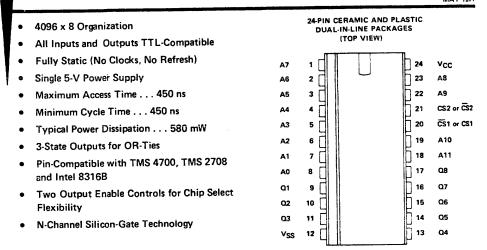

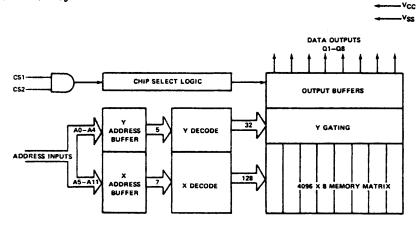

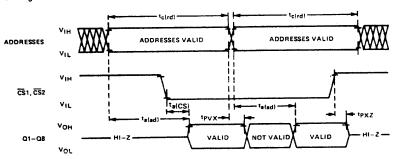

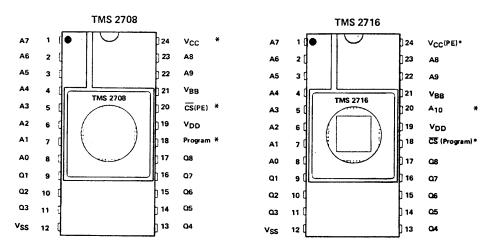

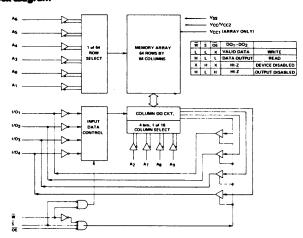

| В | MEMORY DATA SHEETS                                          |

| С | ASCII CODE                                                  |

| Ď | BINARY, DECIMAL AND HEXADECIMAL NUMBERING                   |

| Ē | TMS 9901 PROGRAMMABLE SYSTEMS INTERFACE (DATA MANUAL)       |

| F | TMS 9902 ASYNCHRONOUS COMMUNICATIONS CONTROLLER DATA MANUAL |

| G | TMS 9980A/TMS 9981 MICROPROCESSOR DATA MANUAL               |

| H | TMS 9900 FAMILY MACHINE CYCLES                              |

| ï | DATA TERMINAL HOOKUP                                        |

| J | I/O CABLES AND CONNECTORS                                   |

| K | PARTS LIST                                                  |

|   |                                                             |

# LIST OF ILLUSTRATIONS

| Figure No. | Title                                                                    | Page   |

|------------|--------------------------------------------------------------------------|--------|

| 1-1        | Principal TM 990/189 Components                                          | 1-2    |

| 1-2        | System Block Diagram                                                     | 1-3    |

| 2-1        | Power Supply Hook Up                                                     | 2-1    |

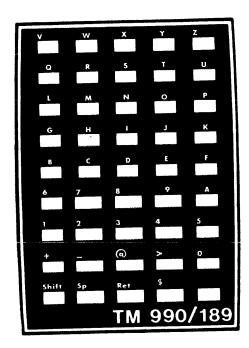

| 2-2        | Unshifted Key Code Designation                                           | 2-3    |

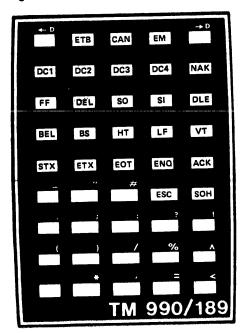

| 2-3        | Shifted Key Code Designation                                             | 2-3    |

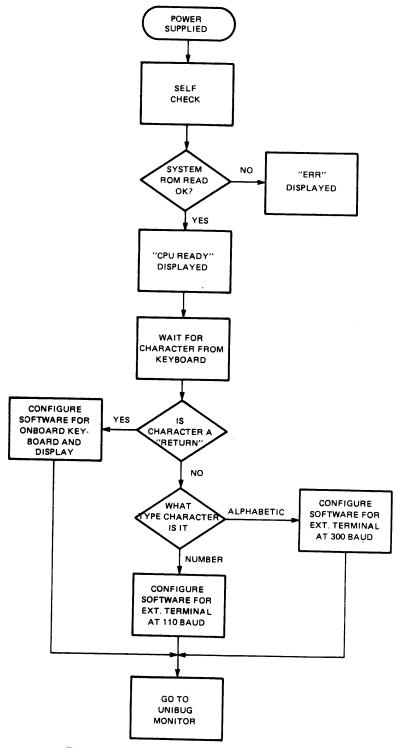

| 2-4        | Power Up Initialization Flow Chart                                       | 2-4    |

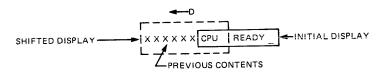

| 2-5        | Display Left Operation                                                   | 2-5    |

| 2-6        | Display Right Operation                                                  | 2-5    |

| 2-7        | External Terminal Hook Up                                                | 2-6    |

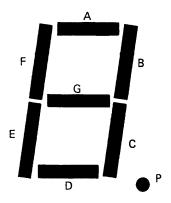

| 2-8        | Display Segment Designation                                              | 2-8    |

| 2-9        | ACI Connector Pins                                                       | 2-9    |

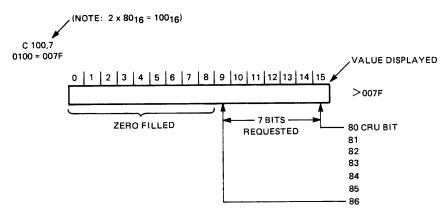

| 3-1        | CRU Bits Inspected By C Command                                          | 3-7    |

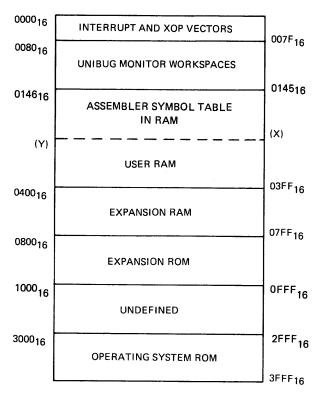

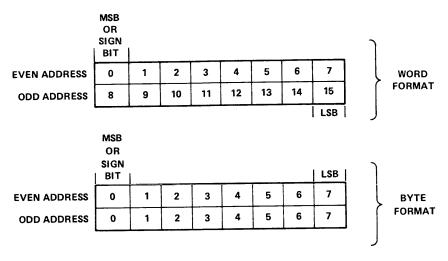

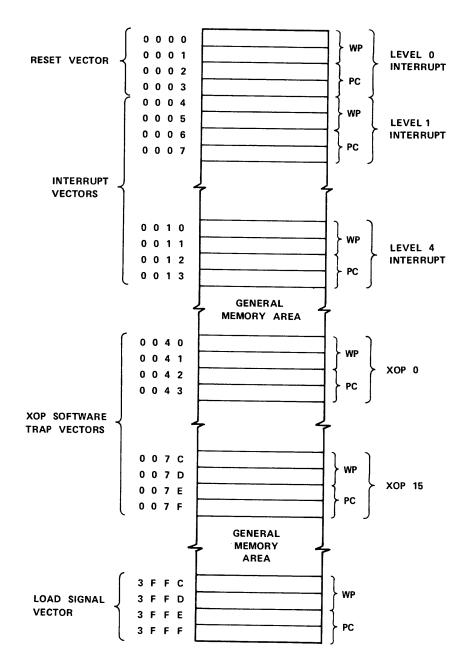

| 5-1        | Memory Map                                                               | 5-2    |

| 5-2        | TMS 9980A With RAM/ROM Memory                                            | 5-3    |

| 5-3        | Status Register                                                          | 5-4    |

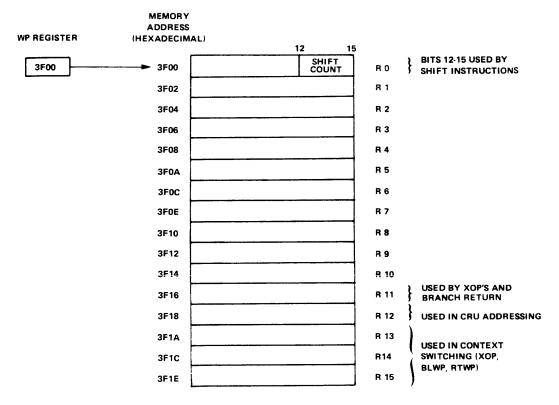

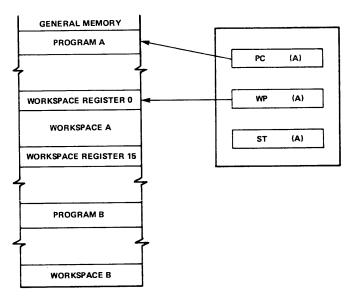

| 5-4        | Workspace Example                                                        | 5-7    |

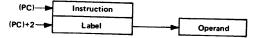

| 5-5        | TM 990/189M Instruction Formats                                          | 5-8    |

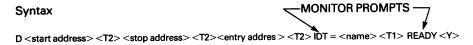

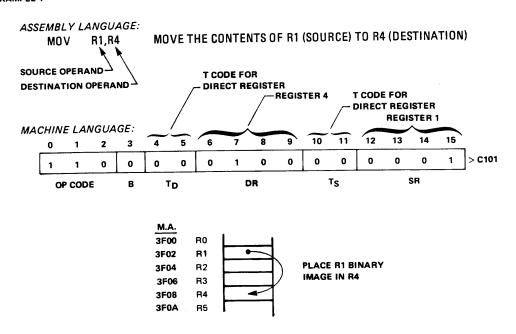

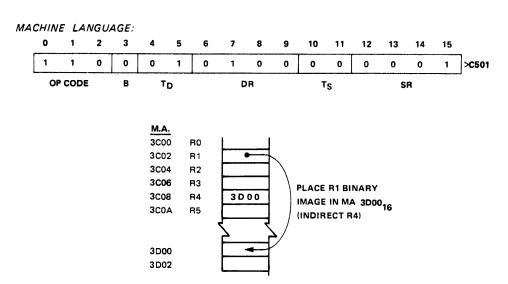

| 5-6        | Direct Register Addressing Examples                                      | 5-13   |

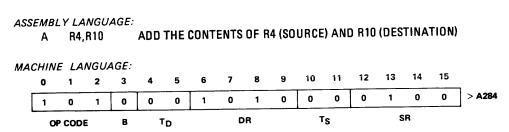

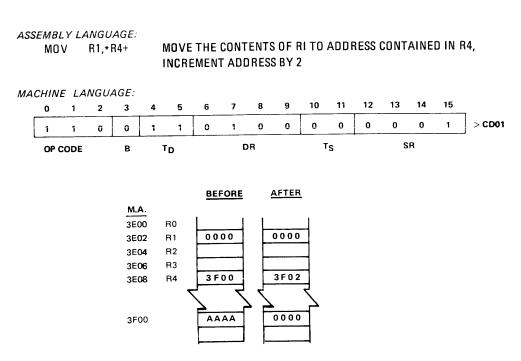

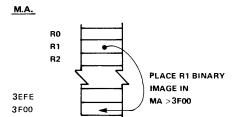

| 5-7        | Indirect Register Addressing Example                                     | 5-14   |

| 5-8        | Indirect Register Autoincrement Addressing Example                       | . 5-15 |

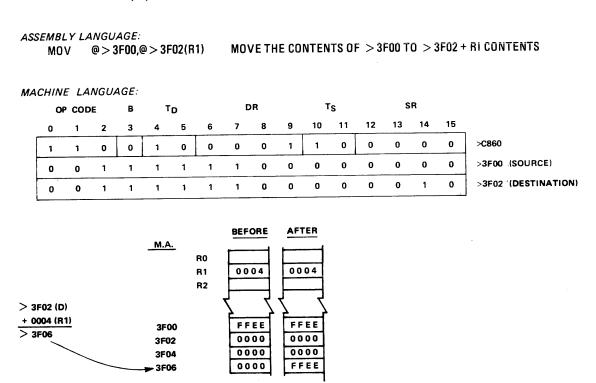

| 5-9        | Symbolic Memory Addressing Examples                                      | 5-16   |

| 5-10       | Symbolic Memory Addressing, Indexed Example                              | 5-17   |

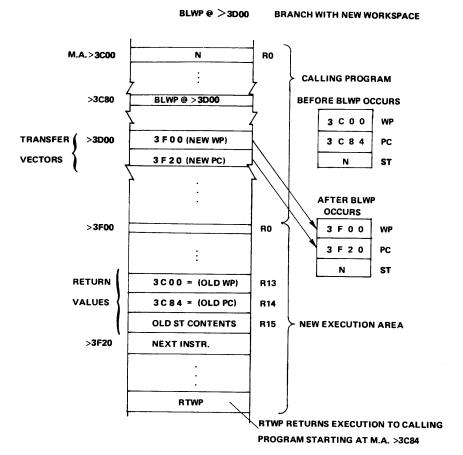

| 5-11       | BLWP Example                                                             | 5-34   |

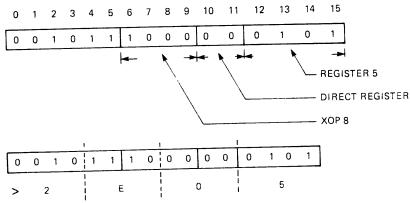

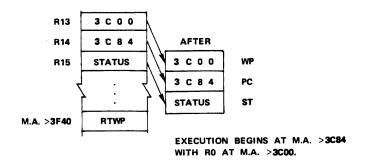

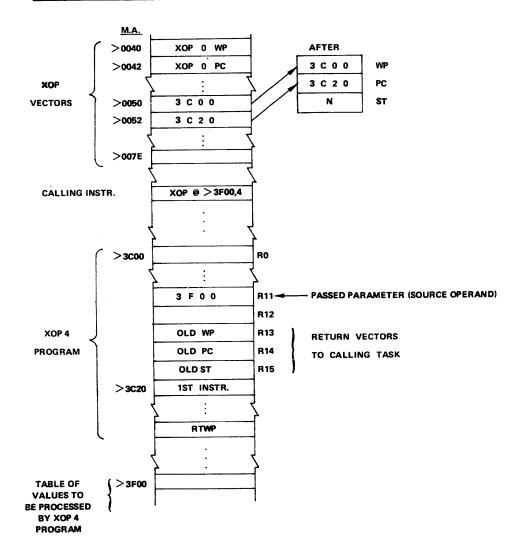

| 5-12       | XOP Example                                                              | 5-39   |

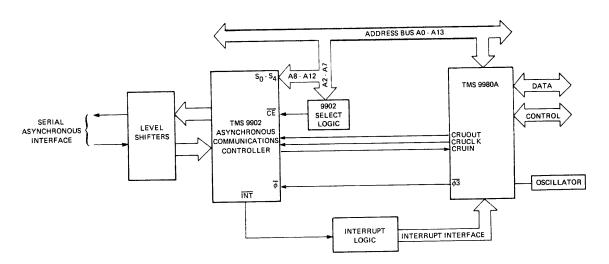

| 7-1        | Typical Application TMS 9902 Asynchronous Communication Controller (ACC) | 7-1    |

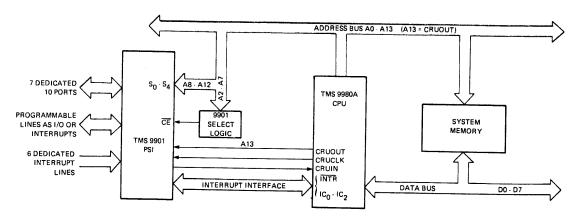

| 7-2        | Typical TMS 9901 Programmable System Interface (PSI) Application         | 7.2    |

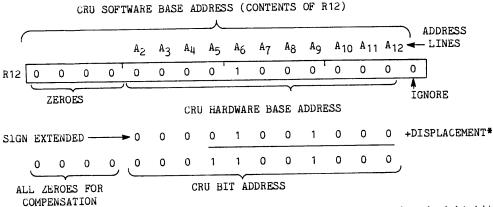

| 7-3        | CRU Address in R12 Vs. Address Bus Lines                                 | 7-3    |

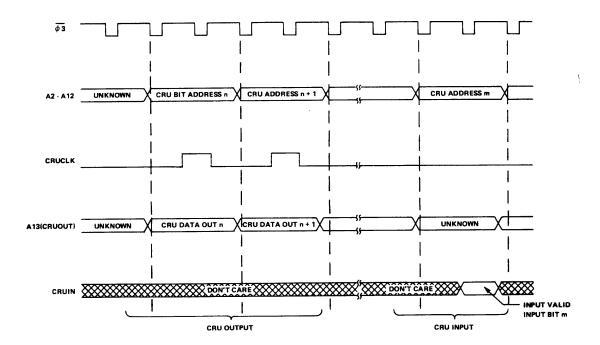

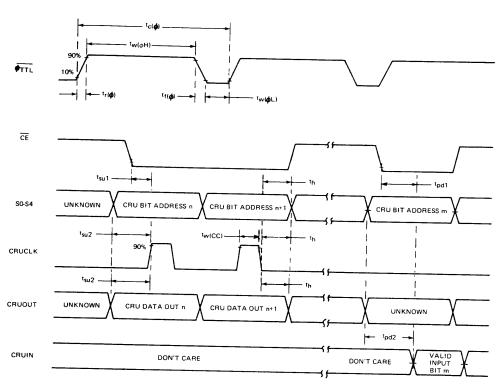

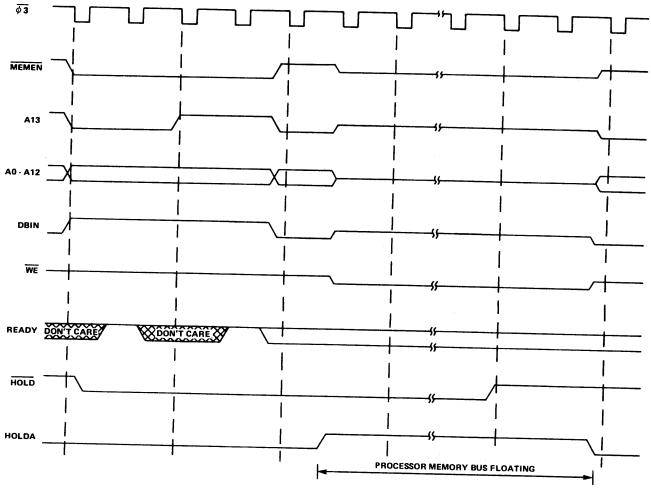

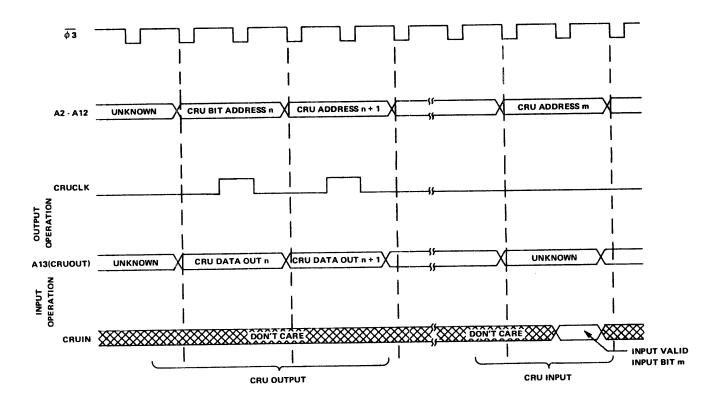

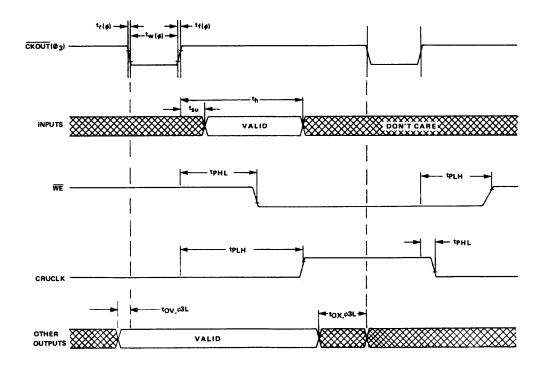

| 7-4        | TMS 9980 CRU Interface Timing                                            | 7-5    |

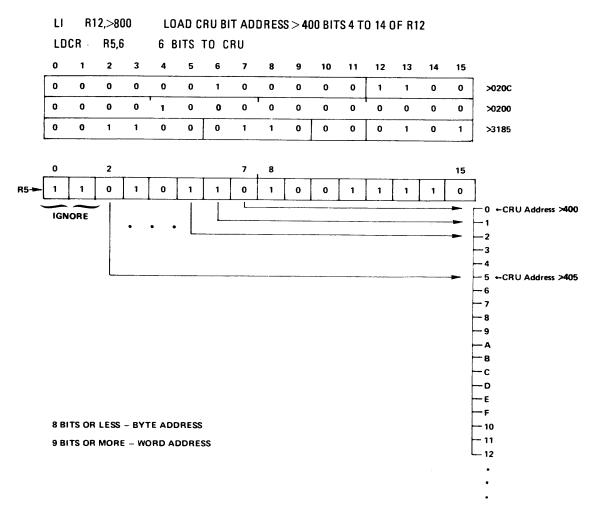

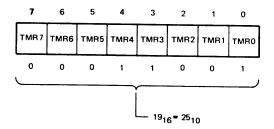

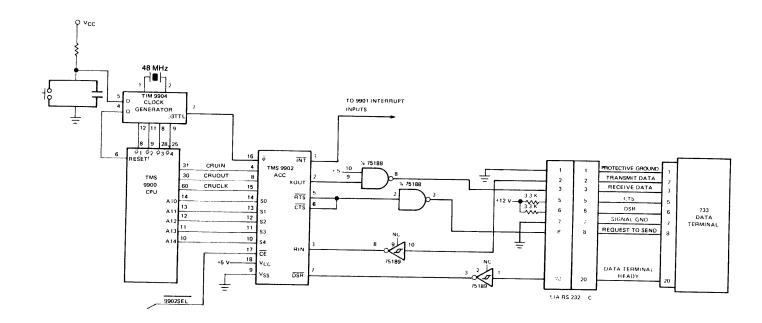

| 7-5        | LDCR Byte Instruction                                                    | 7-6    |

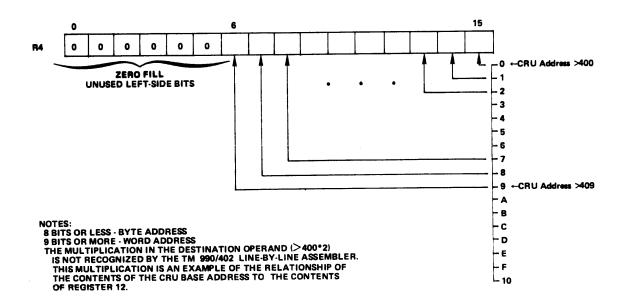

| 7-6        | STCR Word Instruction                                                    | 7-7    |

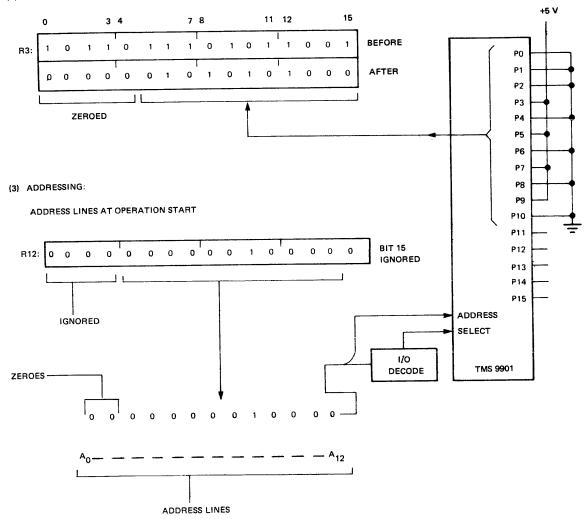

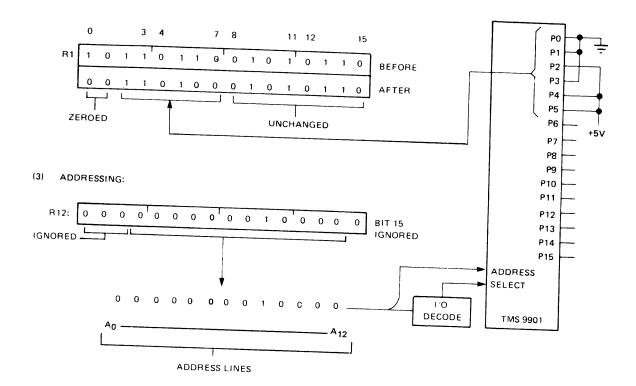

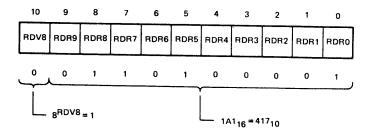

| 7-7        | LDCR Word Execution to TMS 9901                                          | 7-9    |

| 7-8        | LDCR Byte Execution to TMS 9901                                          | 7-10   |

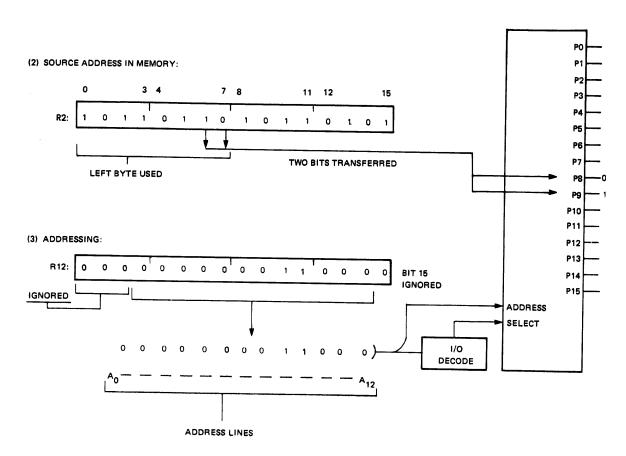

| 7-9        | STCR Word Execution to TMS 9901                                          | 7-11   |

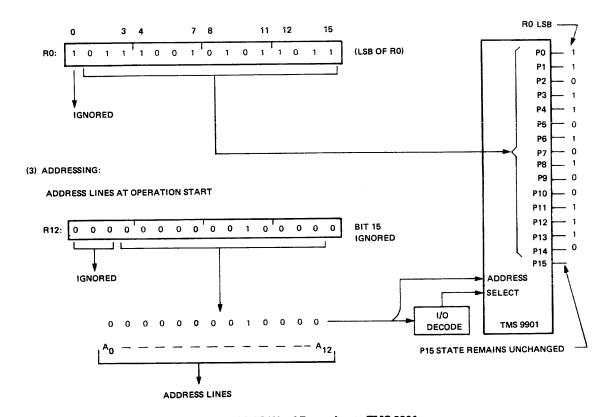

| 7-10       | STCR Byte Execution to TMS 9901                                          | 7-12   |

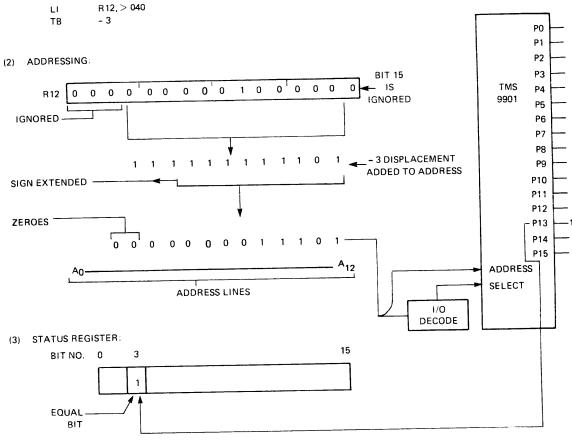

| 7-11       | Test CRU Bit at TMS 9901                                                 | 7-13   |

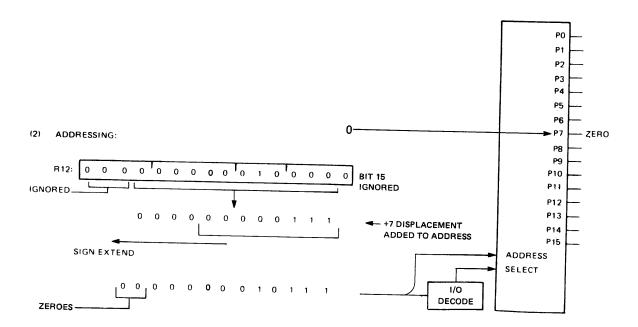

| 7-12       | Set CRU Bit at TMS 9901                                                  | 7-14   |

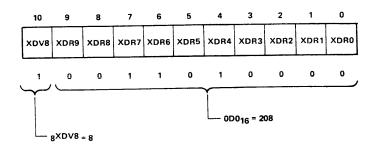

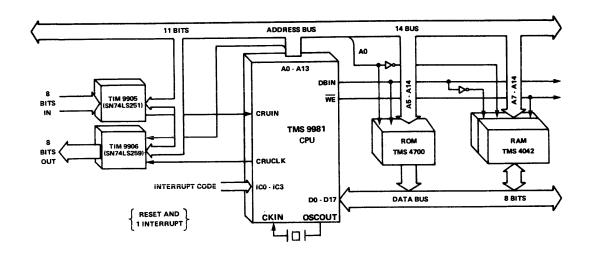

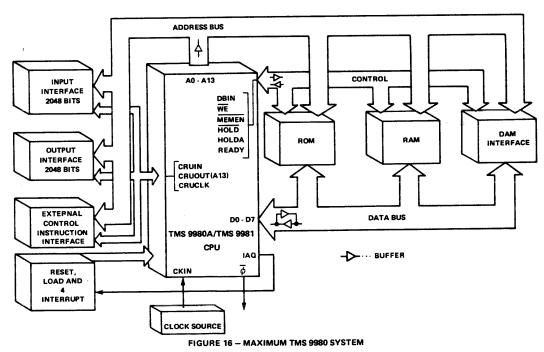

| 8-1        | System Block Diagram                                                     | 8-2    |

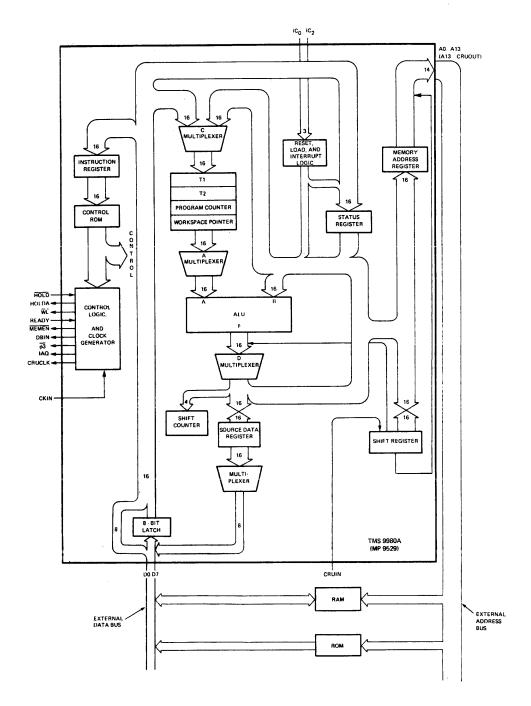

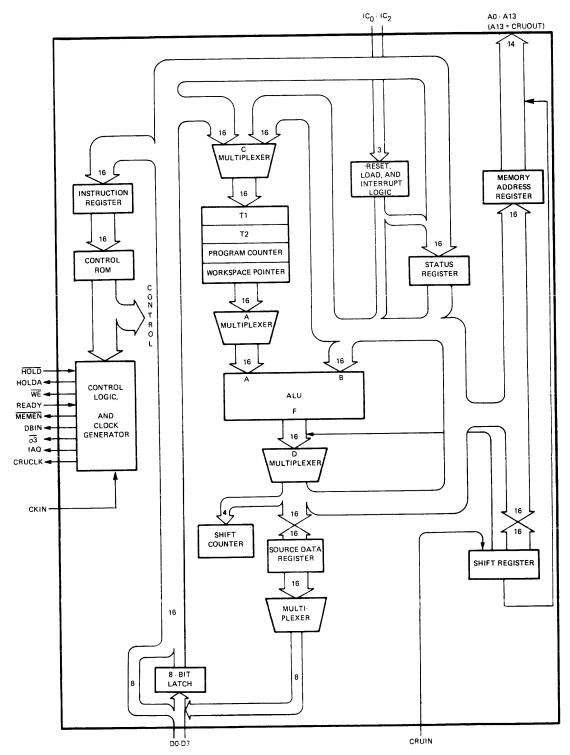

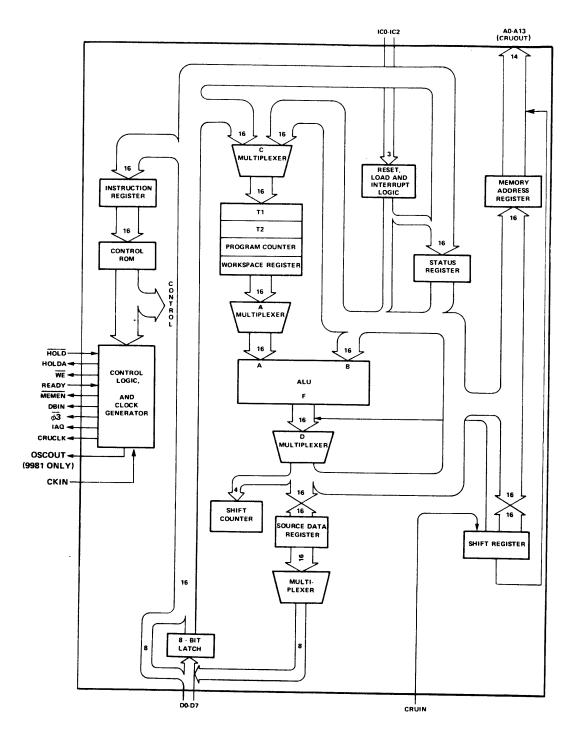

| 8-2        | TMS 9980A Internal Architecture                                          | 8-5    |

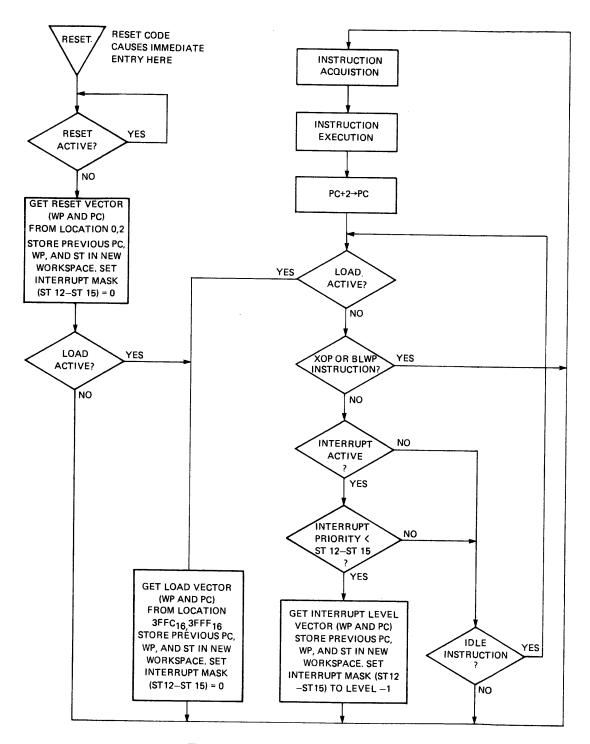

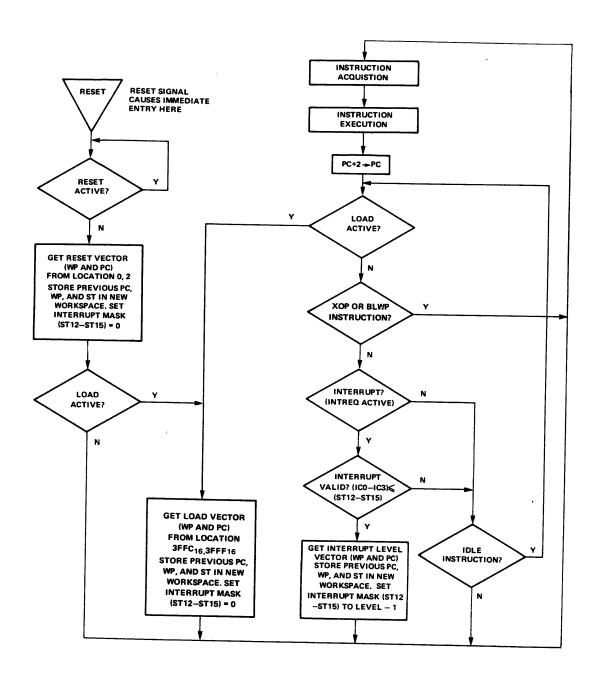

| 8-3        | TMS 9980A CPU Flow Chart                                                 | 8-6    |

| 8-4        | TMS 9980A Signals                                                        | 8.7    |

| 8-5        | External Instruction Decode                                              | 8.7    |

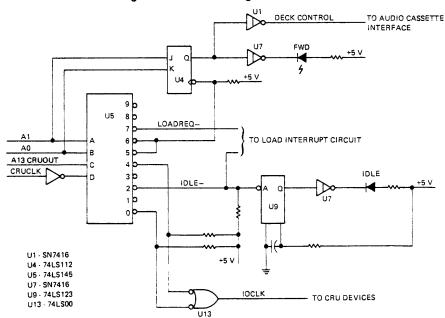

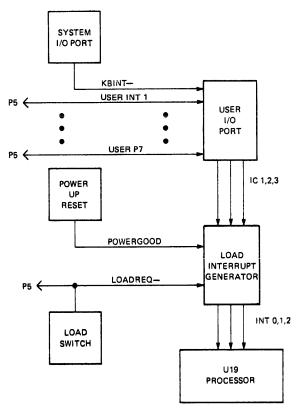

| 8-6        | Interrupt Signal Flow                                                    | 0.0    |

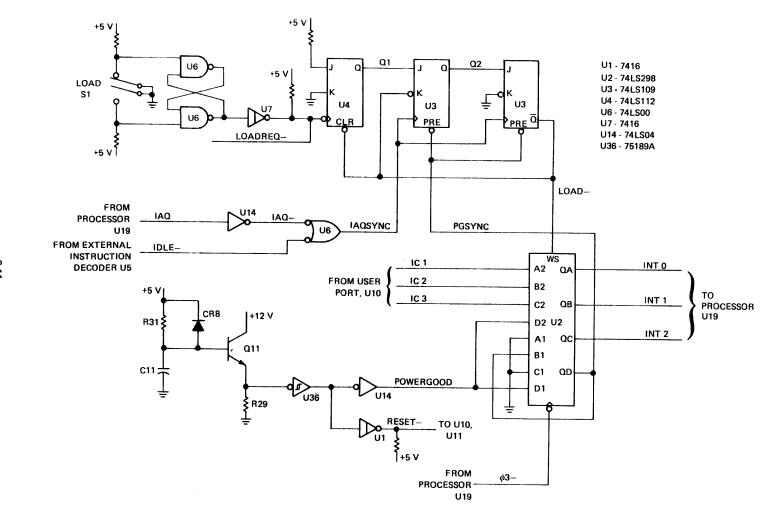

| 8-7        | Load Interrupt Generator and Power Up Reset Circuit                      | Q_11   |

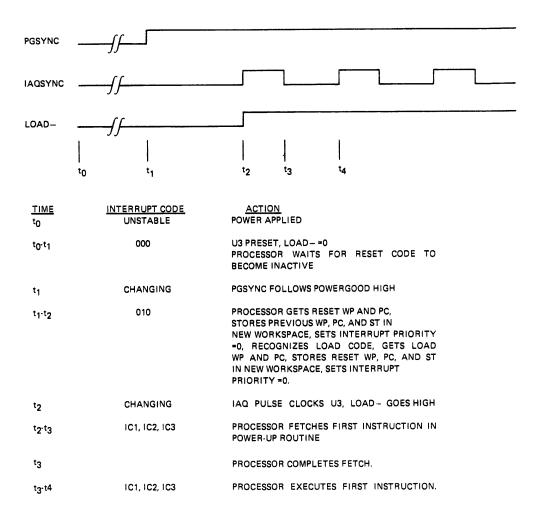

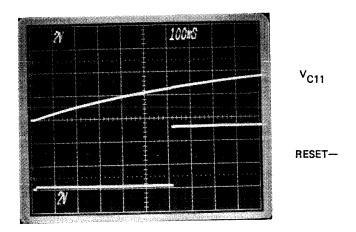

| 8-8        | Power-Up Sequence Timing                                                 | 8-12   |

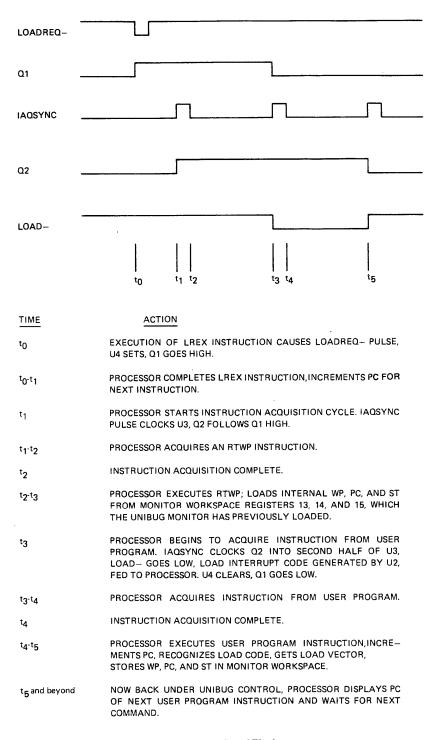

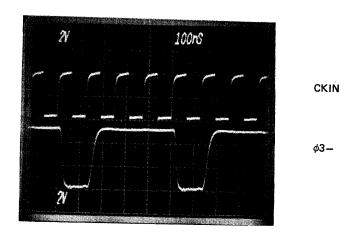

| 8-9        | Load Timing                                                              | 8-13   |

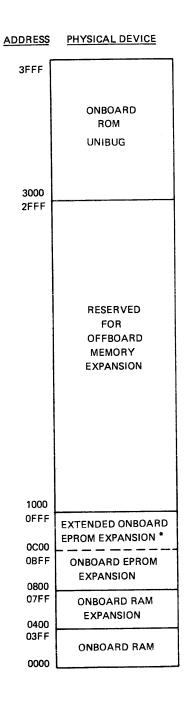

| 8-10       | System Memory Map                                                        | Q_15   |

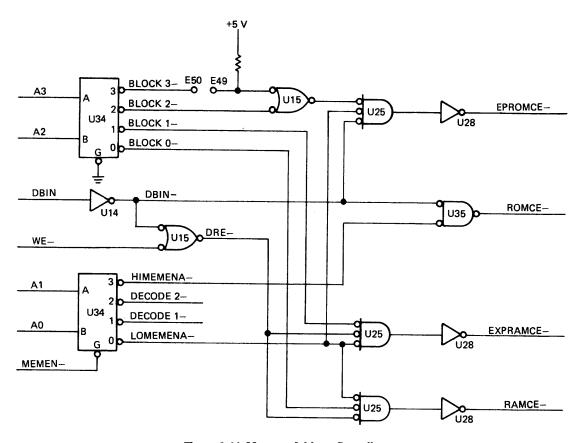

| 8-11       | Memory Address Decoding                                                  | 8-16   |

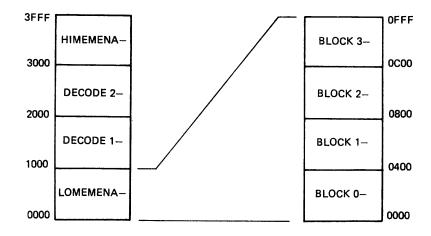

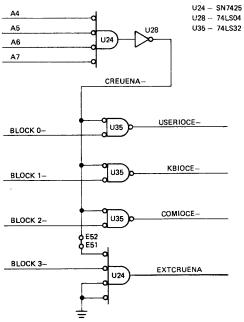

| 8-12       | Memory Partitioning Signals                                              | 8.16   |

# LIST OF ILLUSTRATIONS (Concluded)

| Figure No.                                                                                   | Title                                                                                                                                                                                                                                                                                                                                | Page                                                                                 |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

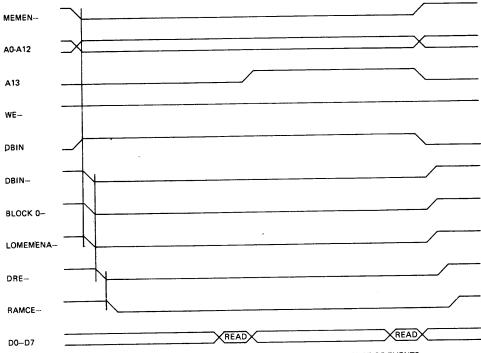

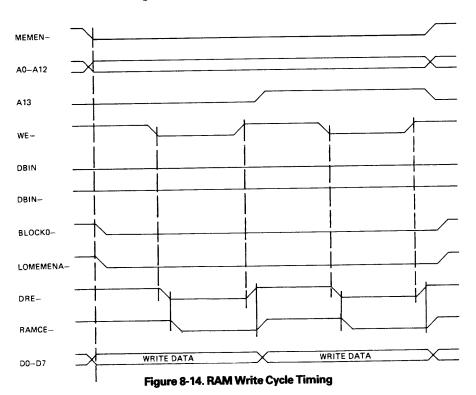

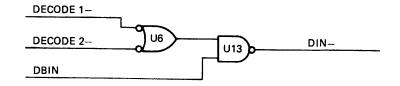

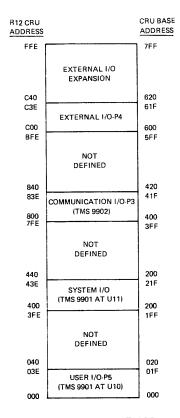

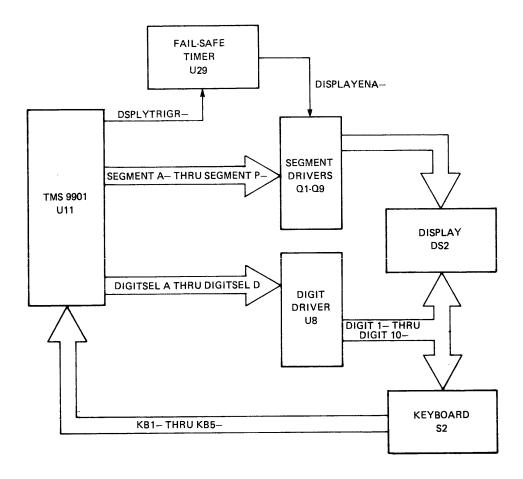

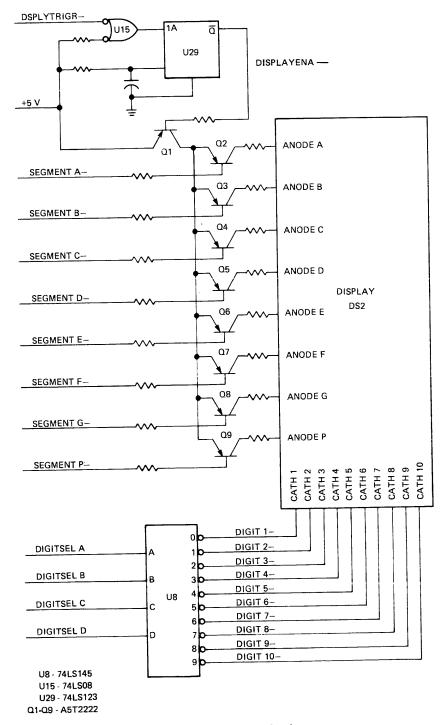

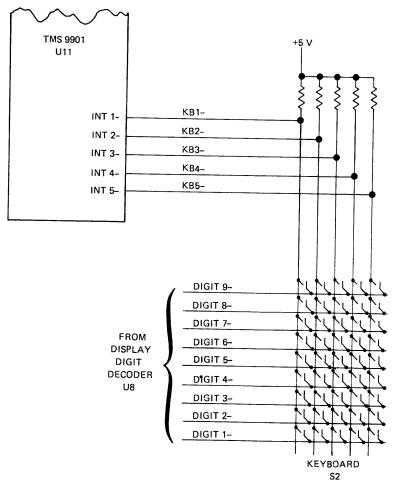

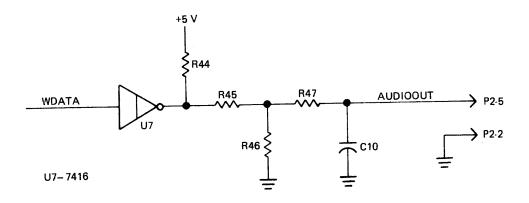

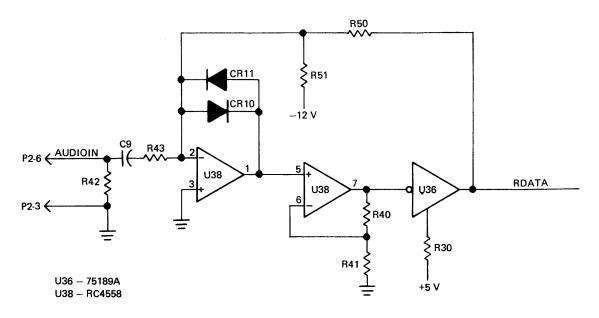

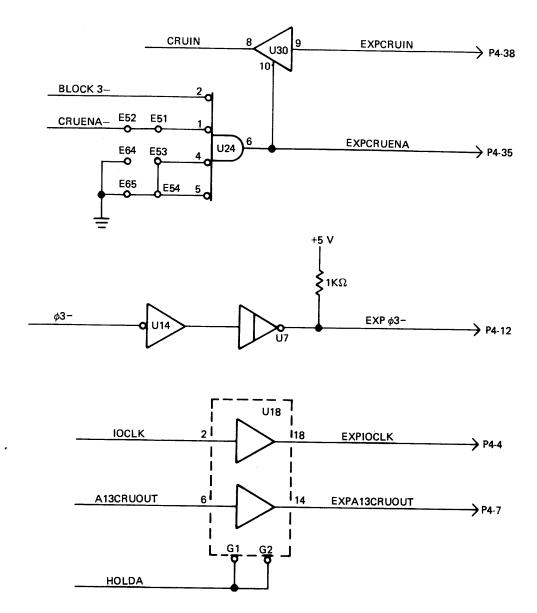

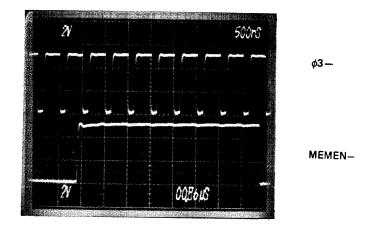

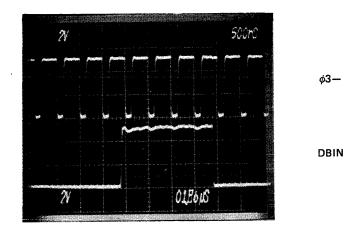

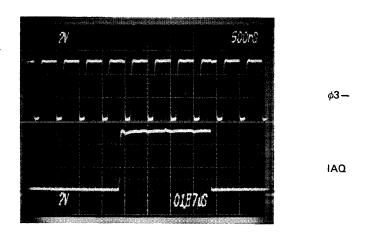

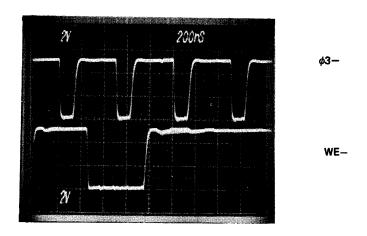

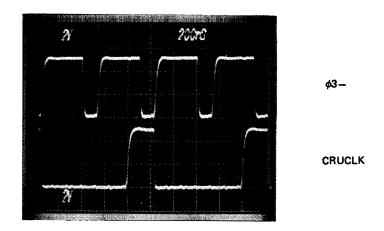

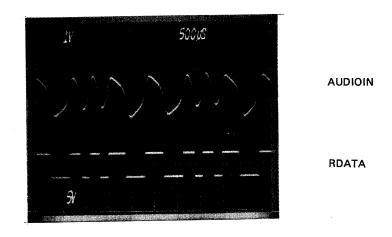

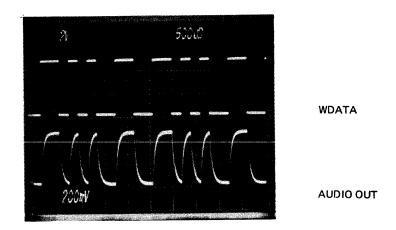

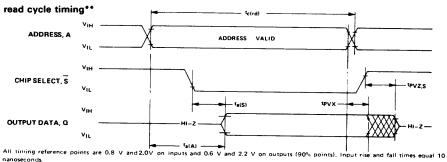

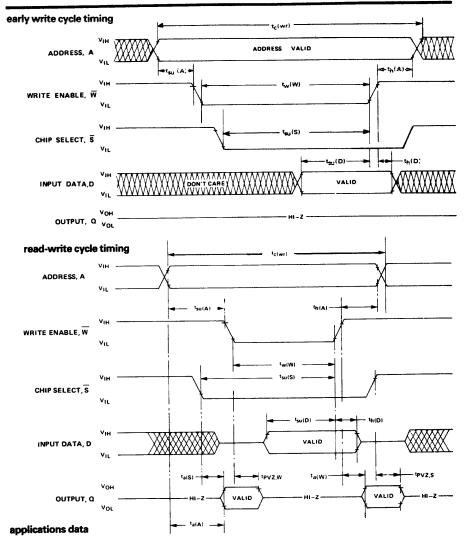

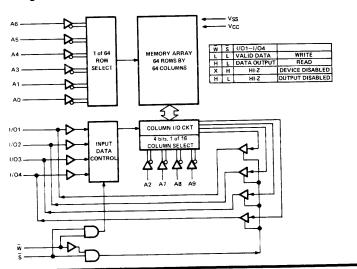

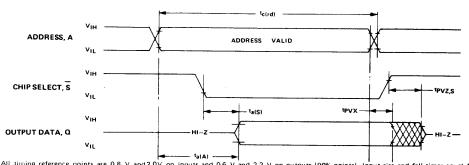

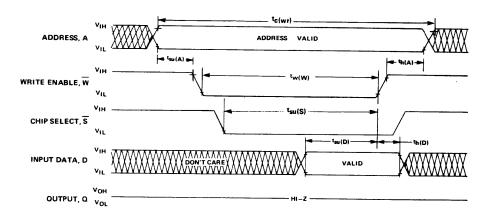

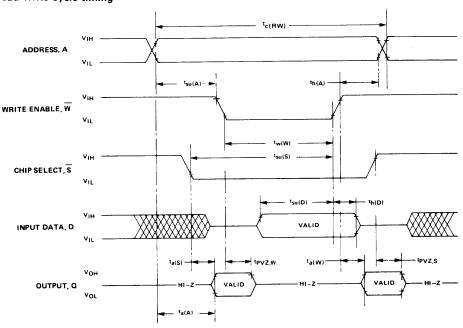

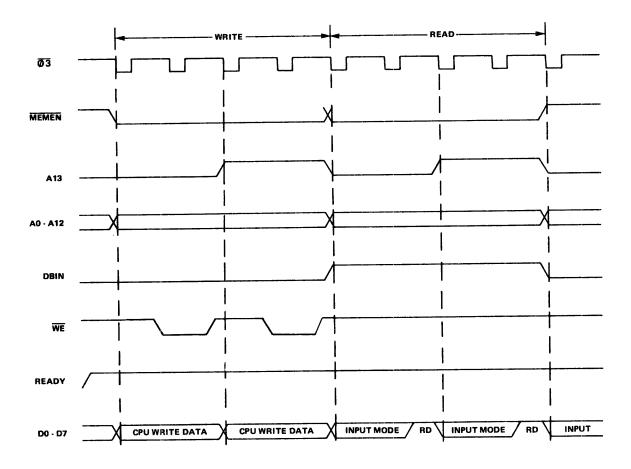

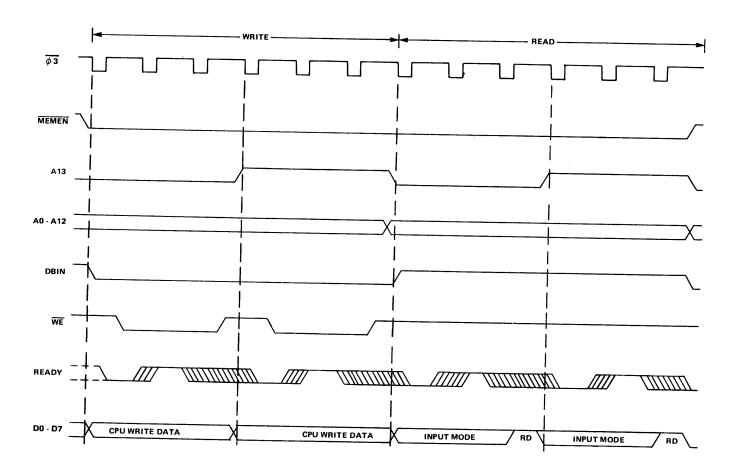

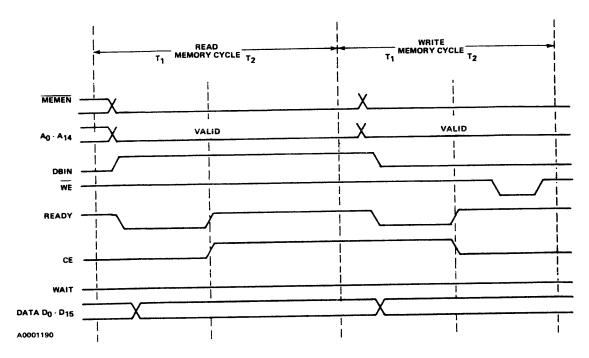

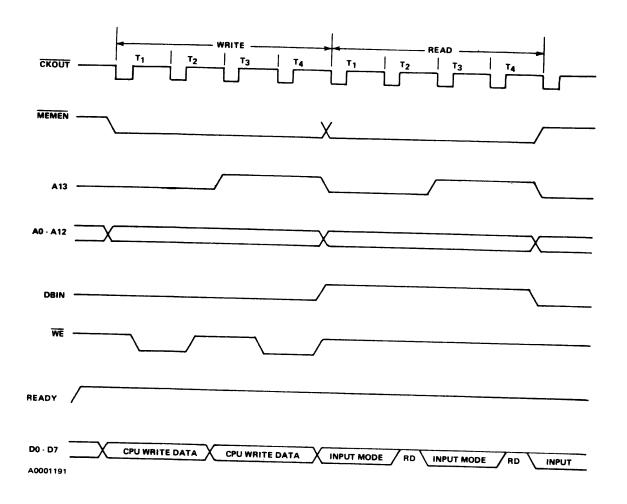

| 8-13<br>8-14<br>8-15<br>8-16<br>8-17<br>8-18<br>8-19<br>8-20<br>8-21<br>8-22<br>8-23<br>8-24 | RAM Read Cycle Timing RAM Write Cycle Timing Expansion Data Bus Control Logic System CRU Map CRU Address Decoding Logic Keyboard and Display Interface Block Diagram Display Segment Designation Display Driver Circuitry Keyboard Interface Cassette Write Circuit Cassette Read Circuit External I/O Port  TM 990/189 Board Layout | 8-17<br>8-18<br>8-19<br>8-19<br>8-21<br>8-21<br>8-23<br>8-24<br>8-25<br>8-26<br>8-28 |

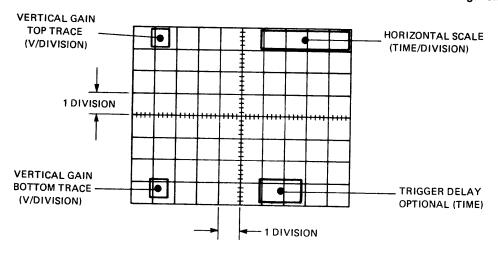

| 10-1                                                                                         | Photo Interpretation Code                                                                                                                                                                                                                                                                                                            |                                                                                      |

|                                                                                              | LIST OF TABLES                                                                                                                                                                                                                                                                                                                       |                                                                                      |

| Table No.                                                                                    | Title                                                                                                                                                                                                                                                                                                                                | Page                                                                                 |

| 2-1<br>2-2<br>2-3                                                                            | Power Supply Requirements  Display Character Font  Recorder and ACI Connections                                                                                                                                                                                                                                                      | . 2-7                                                                                |

| 3-1<br>3-2<br>3-3                                                                            | UNIBUG Commands  Command Syntax Conventions  User Accessible Utilities                                                                                                                                                                                                                                                               | . 3-2<br>3-14                                                                        |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7                                                | Status Bits Affected by Instructions Op Codes (Alphabetical) Op Codes by Format Instruction Description Terms Instruction Set, Alphabetical Index Instruction Set, Numerical Index Comparison of Jumps, Branches, XOP's                                                                                                              | 5-9<br>5-10<br>5-18<br>5-19<br>5-21                                                  |

| 7-1                                                                                          | CRU Address Map                                                                                                                                                                                                                                                                                                                      | . 7-2                                                                                |

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7                                                | Control Bus Functions  External Instruction Results  TMS 9980A Interrupt Decoding Interrupt Sources  User Port I/O Map  System Port I/O Map  Communications I/O Map                                                                                                                                                                  | . 8-8<br>. 8-9<br>8-20<br>8-22<br>8-27                                               |

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5<br>9-6                                                       | List of Materials, Offboard Memory Expansion List of Material, EIA Option List of Materials, TTY Option LED Disconnection Modification Communications Interrupt Modification List of Materials, System Frequency Modification                                                                                                        | . 9-3<br>. 9-4<br>. 9-5<br>. 9-6                                                     |

| 10-1                                                                                         | Supply Voltage Operational Limits                                                                                                                                                                                                                                                                                                    | 10-2                                                                                 |

### **SECTION 1**

### INTRODUCTION

# 1.1 GENERAL

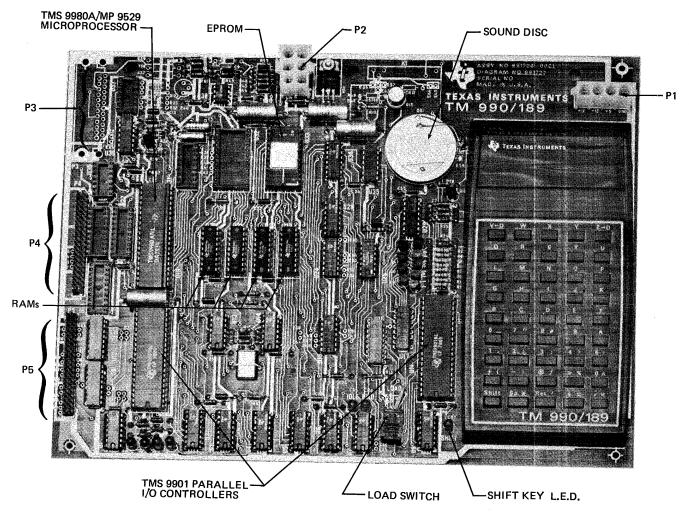

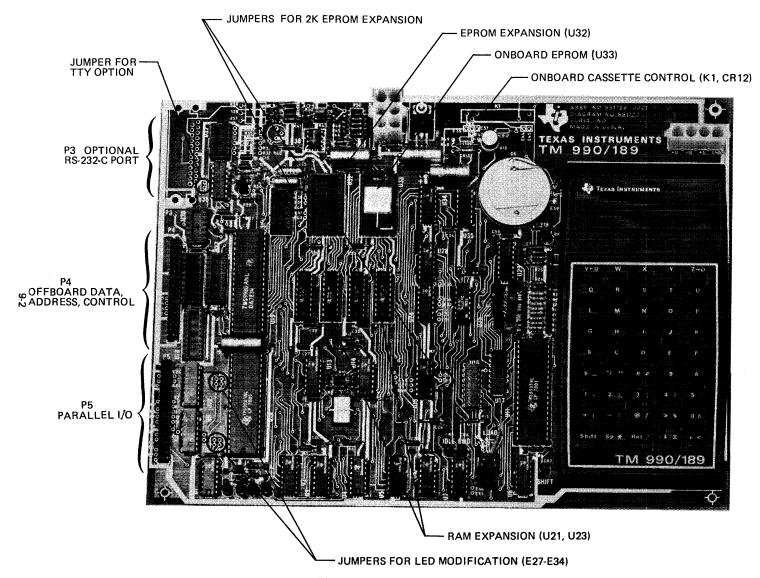

The TM 990/189 is a self-contained, single-board microcomputer system. It is intended for use as a learning aid in the instruction of microcomputer fundamentals, machine and assembly language programming, and microcomputer interfacing. It also demonstrates TMS 9900 family applications and advantages. Figure 1-1 shows the principal TM 990/189 components. The system's features include:

- TMS 9980A (MP9529) microprocessor

- 1024 bytes of random access memory (RAM) expandable on board to 2048 bytes (each byte contains 8 bits of data)

- 4096 bytes of read only memory (ROM) expandable on board to 6144 bytes

- 2 MHz crystal controlled clock

- Audio cassette interface

- 16 bit programmable I/O port and interrupt monitor (TMS 9901)

- 45-key alphanumeric keyboard

- Ten-digit, seven-segment L.E.D. type alphanumeric display

- Visual and acoustic indicators

- Resident system monitor and assembler

- Single step instruction execution

In addition to onboard memory expansion, two other system expansion options are available:

- A TMS 9902 asynchronous communications controller, and accompanying interface circuits for either RS-232-C or 20 mA current loop terminals can be added.

- The bus can be expanded by use of the Bus Interface.

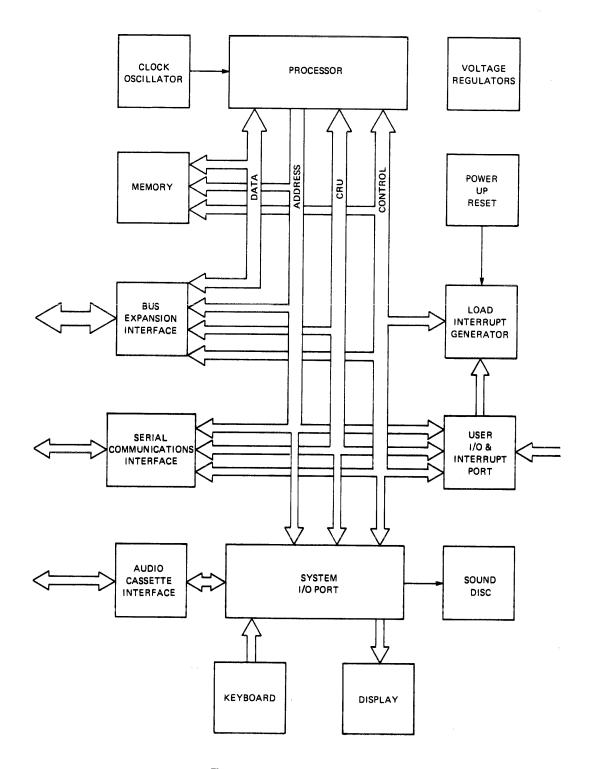

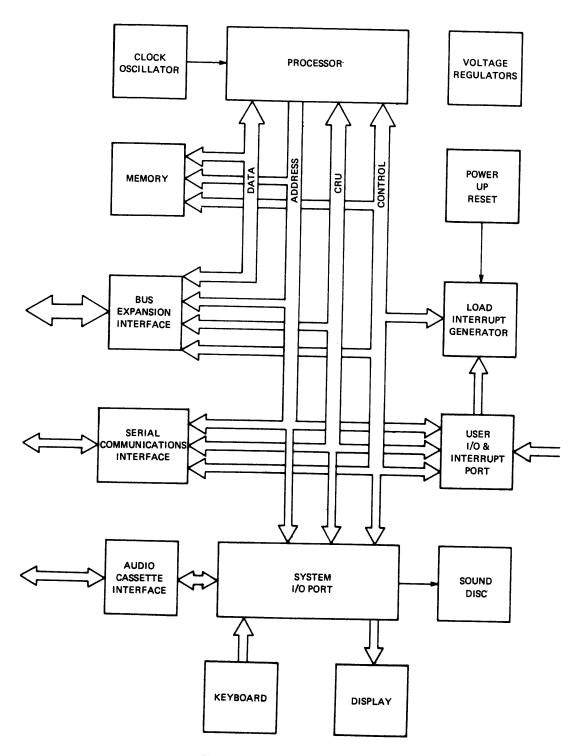

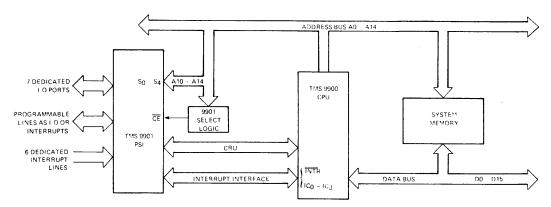

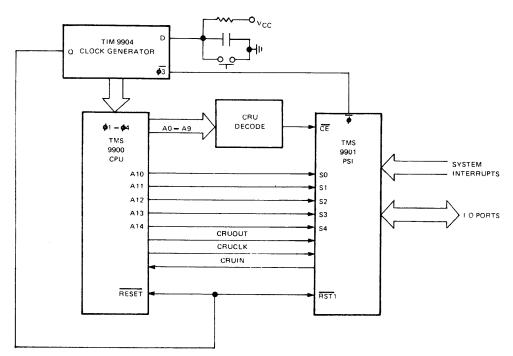

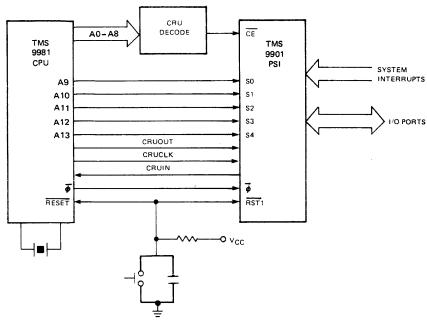

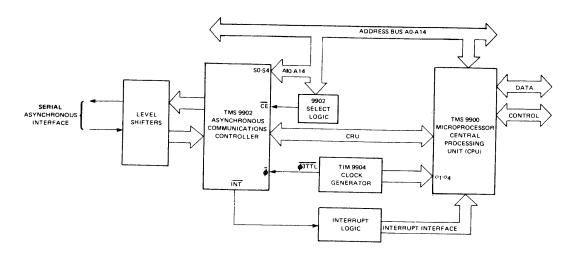

Figure 1-2 shows the system architecture along with the user options.

# 1.2 MANUAL ORGANIZATION

This manual is organized as follows:

- Section 1 covers board specifications and characteristics. A glossary in paragraph 1.4

explains terms used throughout the manual.

- Section 2 shows how to install, power up, and operate the TM 990/189 microcomputer.

Figure 1-1. Principal TM 990/189 Components

Figure 1-2. System Block Diagram

- Section 3 explains the UNIBUG monitor. UNIBUG commands, XOPs and error indicators are topics included.

- Section 4 is an introduction to the Symbolic Assembler used in the TM 990/189.

- Section 5 covers the instruction set used with the TM 990/189. Instruction formats and addressing modes are explained in detail.

- Section 6 covers assembler directives.

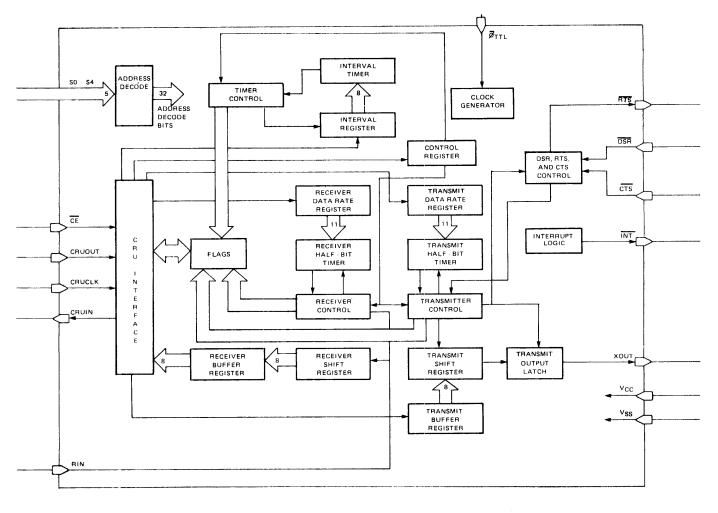

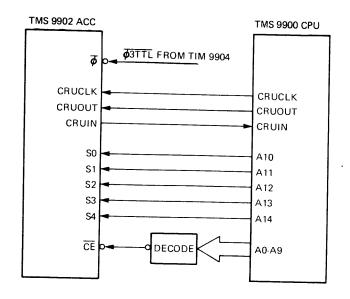

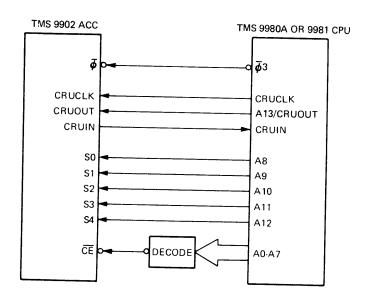

- Section 7 presents the fundamental concepts involved in I/O programming. The Communications Register Unit (CRU) and two interface adaptors (TMS 9901 and TMS 9902) are described along with their programming techniques.

- Section 8 covers theory of operation including memory and I/O mapping, block diagram, and circuit descriptions.

- Section 9 provides the necessary information to utilize the available options and modify the system.

- Section 10 provides a very useful troubleshooting checklist and debugging hints. Both static and dynamic checks are given.

# 1.3 GENERAL SPECIFICATIONS

Power consumption (Typical):

|                                | +5 V   | +12 V  | −12 V  |

|--------------------------------|--------|--------|--------|

| 1024 bytes RAM, 4096 bytes ROM | 595 mA | 76 mA  | 5.6 mA |

| 2048 bytes RAM, 5120 bytes ROM | 701 mA | 121 mA | 36 mA  |

| 2048 bytes RAM, 6144 bytes ROM | 696 mA | 102 mA | 16 mA  |

Clock rate: 2 MHz

Baud rates (set by UNIBUG monitor): 110 baud and 300 baud

Memory size:

RAM (TMS 4014), 1024 bytes expandable on-board to 2048 bytes. (Equivalent RAM is TMS 4045.)

ROM (TMS 4732), 4096 bytes expandable on-board to 6144 bytes.

Board dimensions: 8.15 by 11 inches (20.7 by 27.9 cm)

### 1.4 GLOSSARY

The following are definitions of terms used with the TM 990/189.

Absolute address: The actual memory address in quantity of bytes. Memory addressing is usually represented in hexadecimal from 000016 to 3FFF16 for the TM 990/189.

Alphanumeric character: Letters, numbers, and associated symbols.

ASCII Code: A seven-bit code used to represent alphanumeric characters and control.

Assembler: Program that interprets assembly language source statement into object code.

Assembly Language: Mnemonics which can be interpreted by an assembler and translated into an object program.

Bit: The smallest part of a word; it has a value of either a 1 or 0.

Breakpoint: Memory address where a program is intentionally halted. This is a program debugging tool.

Byte: Eight bits or half a word.

Carry: A carry occurs when the most-significant bit is carried out in an arithmetic operation (i.e., resultant cannot be contained in only 16 bits).

Central Processing Unit (CPU): The "heart" of the computer: responsibilities include instruction access and interpretation, arithmetic functions, I/O memory access. The TMS 9980A (MP9529) is the CPU of the TM 990/189.

Command Scanner: A given set of instructions in the UNIBUG monitor which takes the user's input from the terminal and searches a table for the proper code to execute.

Context Switch: Change in program execution environment, includes new program counter (PC) value and new workspace area.

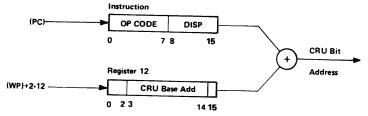

CRU (Communications Register Unit): The TMS 9980A's general purpose, command-driven input/output interface. The CRU provides up to 2048 directly addressable input and output bits.

Effective Address: Memory address resulting from interpretation of an instruction, required for execution of that instruction.

EPROM: See Read Only Memory.

Hexadecimal: Numerical notation in the base 16.

Immediate Addressing: An immediate or absolute value (16-bits) is part of the instruction (second word of instruction).

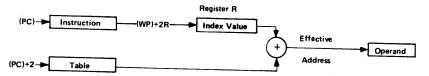

Indexed Addressing: The effective address is the sum of the contents of an index register and an absolute (or symbolic) address.

Indirect Addressing: The effective address is the contents of a register.

Interrupt: Context switch in which new workspace pointer (WP) and program counter (PC) values are obtained from one of 4 interrupt traps in memory addresses 000016 to 001216.

I/O: The input/output lines are the signals which connect an external device to the data lines of the TMS 9980A.

Least Significant Bit (LSB): Bit having the smallest value in a byte or word (smallest power of base 2); represented by the right-most bit.

Link: The process by which two or more object code modules are combined into one, with cross-referenced label address locations being resolved.

Loader: Program that places one or more absolute or relocatable object programs into memory.

Machine Language: Binary code that can be interpreted by the CPU.

Monitor: A program that assists in the real-time aspects of program execution such as operator command interpretation and supervisor call execution. Sometimes called supervisor.

Most Significant Bit (MSB): Bit having the most value in a byte or word; the left-most bit representing the highest power of base 2. This bit is sometimes used to show sign with a 1 indicating negative and a 0 indicating positive.

Object Program: The hexadecimal interpretations of source code output by an assembler program. This is the code executed when loaded into memory.

One's Complement: Binary representation of a number in which the negative of the number is the complement or inverse of the positive number (all ones become zeroes, vice versa). The MSB is one for negative numbers and zero for positive. Two representations exist for zero: all ones or all zeroes.

Op Code: Binary operation code interpreted by the CPU to execute an instruction.

Overflow: An overflow occurs when the result of an arithmetic operation cannot be represented in two's complement (i.e., in 15 bits plus sign bit).

Parity: Means for checking validity of a series of bits, usually a byte. Odd parity means an odd number of one bits; even parity means an even number of one bits. A parity bit is set to make all bytes conform to the selected parity. If the parity is not as anticipated, an error flag can be set by software. The parity jump instruction can be used to determine parity.

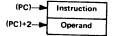

Program Counter (PC): Hardware register that points to the next instruction to be executed or next word to be interpreted.

PROM: See Read Only Memory.

Random Access Memory (RAM): Memory that can be written to as well as read from (vs. ROM).

Read Only Memory (ROM): Memory that can only be read from (can't change contents). Some can be programmed (PROM) using a PROM Programmer. Some PROM's can be erased (EPROM's) by exposure to ultraviolet light.

Source Program: Programs written in mnemonics that can be translated into machine language (by an assembler).

Status Register (ST): Hardware register that reflects the outcome of a previous instruction and the current interrupt mask.

Supervisor: See Monitor.

Utilities: A unique set of instructions used by different parts of the program to perform the same function. In the case of UNIBUG, the utilities are the I/O XOP's.

Word: Sixteen bits or two bytes.

Workspace Register Area: Sixteen words, designated registers 0 to 15, located in RAM for use by the executing program.

Workspace Pointer (WP): Hardware register that contains the memory address of the beginning (register 0) of the workspace area.

# 1.5 APPLICABLE DOCUMENTS

The following is a list of documents that provide supplementary information for the TM 990/189 user.

- TMS 9901 Programmable Systems Interface Data Manual

- TMS 9902 Asynchronous Communication Controller (Data Manual)

- TMS 9980A/TMS 9981 Microprocessor Data Manual

- TMS 9900 Family System Development Manual

# **SECTION 2**

# INSTALLATION AND OPERATION

# 2.1 GENERAL

This section covers power supply requirements, power up procedure, operation (keyboard and display), and use of the audio cassette interface.

# 2.2 REQUIRED EQUIPMENT

- TM 990/189 University Board

- Suitable power supply such as TM 990/519

An equivalent power supply capable of meeting the requirements given in Table 2-1 may be used.

TABLE 2-1. POWER SUPPLY REQUIREMENTS

| Voltage | Regulation | CURRENT |

|---------|------------|---------|

| +5 V    | +/-5%      | 1.787 A |

| +12 V   | +/-5%      | 0.214 A |

| -12 V   | +/-5%      | 0.155 A |

# 2.3 POWER UP PROCEDURE

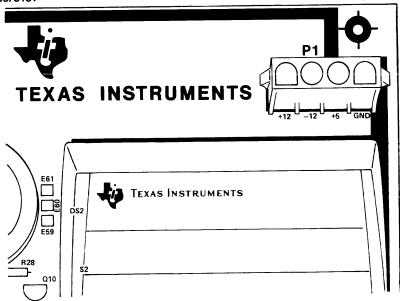

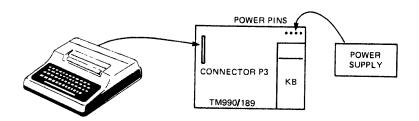

Figure 2-1 shows how to connect voltage to the TM 990/189 board. A cable is supplied which directly facilitates connection of the TM 990/189 to a TM 990/519 power supply. The connections on each end are positively keyed and prohibit misconnection of the power supply. Also, since the connectors are identical and this cable is wired "one for one," either end may be connected to the TM 990/189 or the TM 990/519.

Figure 2-1. Power Supply Hook Up

When using a power supply other than the TM 990/519, the user should remove one connector from the cable and attach the proper connector or plugs for the power supply to be used. The power cable conductors are color coded as follows:

+5 V - Red

+12 V - White

-12 V - Green

Ground - Black

### NOTE

It is advisable to check the connections from the TM 990/189 to the power supply output terminals with an ohmmeter before applying power.

### **CAUTIONS**

- Avoid applying incorrect voltage levels to the TM 990/189. Texas Instruments assumes no responsibility for damage caused by improper wiring or voltage application by the user.

- Do not operate the TM 990/189 board on metal or other conductive surfaces without use of a protective insulator between the two.

### 2.4 OPERATION

- Verify that all wiring has been correctly connected.

- 2. Apply power to board.

- 3. The TM 990/189 has a power up load feature. The system initialization routine performs a self-check operation on the major system components and indicates a successful self-check completion by displaying "CPU READY" in the display.

# 2.5 KEYBOARD

# 2.5.1 KEYBOARD DESCRIPTION

The keyboard consists of 45 keys. Figure 2-2 and Figure 2-3 show the unshifted and shifted key code designations respectively. Keys are shifted when the SHIFT key is depressed; while in this mode, the shift L.E.D. will illuminate. The keyboard becomes unshifted as soon as any key is pressed with the exception of DISPLAY RIGHT  $(\rightarrow D)$  or DISPLAY LEFT  $(\leftarrow D)$ .

### 2.5.2 KEYBOARD USE

The keyboard is used to enter commands and data to the microprocessor. The TM 990/189 will energize in a power up LOAD state and the display will show CPU READY. At this point the microprocessor will wait for one character to be input. If the character is P, the TM 990/189 will be configured to receive data from a terminal (assuming that the User I/O and Interrupt Port modifications have been made as described in Section 4). If the RETURN (Ret) key is pressed, the microprocessor is configured to accept data from the keyboard. The display will show a question mark indicating that the command scanner is available to interpret keyboard inputs. A flowchart covering power up initialization is given in Figure 2-4.

Figure 2-2. Unshifted Key Code Designation

Figure 2-3. Shifted Key Code Designation

Fig. 2-4. Power Up Initialization Flow Chart

### 2.5.3 SPECIAL KEYS DESCRIPTION

# 2.5.3.1 Shift

The SHIFT key carries out the same function as that carried out by the shift key on a typewriter: it invokes a secondary definition for each key on the keyboard. The shift indicator L.E.D. (shown in Figure 1-1) will be activated to indicate that the shift mode has been entered. The shift mode may be exited by pressing any key except DISPLAY RIGHT or DISPLAY LEFT.

# 2.5.3.2 Display Left (←D)

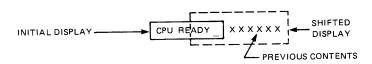

The Display LEFT key shifts the field of view of the display to the left six character positions in the display buffer. This key does not change the contents of the display buffer. Figure 2-5 illustrates the operation of this key.

Figure 2-5. Display Left Operation

# 2.5.3.3 Display Right (→D)

The DISPLAY RIGHT key shifts the field of view of the display to the right six character positions in the display buffer. This key does not change the contents of the display buffer. Figure 2-6 illustrates the operation of this key.

Figure 2-6. Display Right Operation

# 2.5.3.4 External Terminal Use.

The receipt of an alphabetic or numeric character when "CPU READY" is displayed will cause the TM 990/189 to be configured for communication with the optional TMS 9902 Serial Communications Controller and transfers control to the remainder of the system monitor (see Figure 2-4.)

EXAMPLE: Using the TM 990/189 with an External Terminal\*

<sup>\*</sup>See Section 8 for an explanation detailing the installation of the serial communications port and interface circuitry.

### Procedure:

- 1. Plug in the cable from the terminal to connector P3 on the TM 990/189 (See Figure 2-7).

- Connect the power supply cable from the TM 990/189 power pins to the TM 990/519 power supply.

Figure 2-7. External Terminal Hook Up

- Apply power to the system.

- Turn terminal power on.

- Place terminal ON LINE.

- Turn power supply on.

- The TM 990/189 will energize in a power up LOAD state and the display will show CPU READY.

- For communications at 110 baud (10 characters per second) press a numeric key (0 through 9) on the TM 990/189. for communications at 300 baud (30 char/sec) press an alphabetic key (A through Z).

- 6. UNIBUG prints a "?" prompt. The terminal is now ready for use.

### 2.5.3.5 LOAD Switch.

The LOAD switch (S1) activates circuitry on the board which generates a non-maskable load interrupt to the processor. Activating the load switch causes the processor to discontinue execution of the current program and pass control to the UNIBUG monitor. Load switch activation does not alter the contents of user memory.

Since the processor cannot ignore the load stimulus, the load switch provides the user with ultimate control over processor actions. Should program control ever be lost (e.g., if the processor gets caught in an infinite loop) pressing LOAD forces control back to UNIBUG where the user can enter commands and direct system operation.

TABLE 2-2. DISPLAY CHARACTER FONT

| ASCII CHARACTER                         | TABLE 2-2. DISPLAY CHARACTER FONT |            |           |        |                    |               |

|-----------------------------------------|-----------------------------------|------------|-----------|--------|--------------------|---------------|

| B                                       |                                   |            |           |        |                    |               |

| B                                       | Α                                 | R          | a,b,c,e,f | 6      | <u> </u>           | a,c,d,e,f,g   |

| C                                       |                                   | 1          |           | 7      | <u> </u>           | a,b,c         |

| D                                       |                                   |            |           | 8      | 별                  | a,b,c,d,e,f,g |

| F                                       |                                   | ₫          |           | 9      | 닠                  | a,b,c,d,f,g   |

| I                                       |                                   | Ε          |           | 0      | IJ                 | a,b,c,d,e,f   |

| I                                       |                                   | F          |           | SPACE  |                    | (none)        |

| I                                       |                                   |            |           | 6      | Ë                  | a,b,d,e,f,g   |

| J                                       |                                   | 님          |           | \$     | <b>'</b> -!•       | a,c,d,f,p     |

| J                                       |                                   | 1          |           | *      | -¦•                | b,c,g,p       |

| K                                       |                                   | J          |           | i      | -                  | b             |

| L                                       |                                   |            |           | >      | 7                  | a,b           |

| M                                       |                                   | <u> </u>   |           | +      | $\dashv$           | b,c,g         |

| N                                       |                                   | _          |           | -      | -                  | g             |

| O                                       |                                   |            |           | (      | C                  | d,e,g         |

| P                                       |                                   |            |           | )      | コ                  | c,d,g         |

| Q                                       |                                   | P          |           | %      | ا <sup>ــا</sup> • | b,e,g,p       |

| R                                       |                                   | 딕          |           | /      | <u></u>            | b,e,g         |

| S                                       |                                   | _          |           | =      | Ξ                  | d,g           |

| T                                       |                                   | <u>ا _</u> |           | ^      |                    | a,b,f         |

| U                                       |                                   | F          |           | <      | C                  | a,f,g         |

| V = b.d.f.g                             |                                   |            |           | ,      | •                  | d,p           |

| W                                       |                                   | ij         |           | •      | •                  | р             |

| X                                       |                                   | =          |           | ;      | <b></b>   •        | c,d,p         |

| Y                                       |                                   | Ξ          |           | :      | l<br>•             | c,p           |

| Z                                       |                                   | 딕          |           | ?      | ₽.                 | a,b,e,g,p     |

| 1   b,c                                 |                                   | Fi         |           | !      | 1                  | b,c,p         |

| 2                                       | 1                                 | -          |           |        | _                  | d             |

| 3 3 a,b,c,d,g # 5 b,c,d,g 4 b,c,f,g     | 1                                 | į          |           | -<br>n | ñ                  | b,f           |

| 4 b,c,f,g                               | L                                 | Ę          |           | #      |                    | b,c,d,g       |

| 1 4 ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' | l l                               | Ÿ          |           |        |                    |               |

| 5 a,c,d,f,g                             |                                   | Ġ.         |           |        |                    |               |

### 2.6 L.E.D. DISPLAY

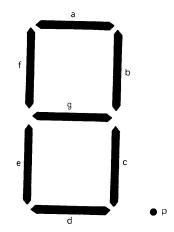

The display is a ten-digit, seven-segment L.E.D. type. It is used to display data, instructions, and error messages. The display segment designation is given in Figure 2-8. Table 2-2 shows display character font. The font gives the ASCII character, the display character, and the segments illuminated.

Figure 2-8. Display Segment Designation

# 2.7 USING AUDIO CASSETTE INTERFACE (ACI)

An audio cassette recorder can be used as a storage medium for programs used with the TM 990/189. The TM 990/189 provides audio cassette interface circuitry and optional user installed recorder control circuitry. The ACI theory of operation is covered in Section 8.

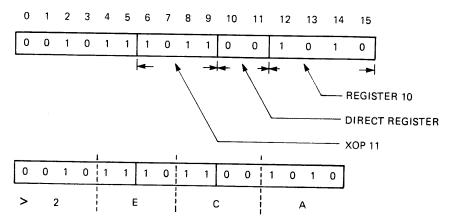

The TM 990/189 monitor provides two commands for use with a recorder. These commands are the L (load memory from cassette) and D (dump memory to cassette). Following entry of the L command, software will activate the motor control bit and begin looking for data from the audio cassette interface. Software will synchronize with the data, convert the data into proper digital format, and deposit the data in memory. After the data is loaded, the motor control bit is deactivated and the module identifier displayed. After entry of the D command and the parameters, the monitor will respond with READY and wait for a "Y" (yes) input from the keyboard. Upon receipt of the "Y" ready acknowledgement, the motor control bit is activated and an appropriate time allowed for the cassette deck to reach operating speed. Memory will be dumped from the start address to the stop address in 990 object record format. Following completion of the memory jump, the motor control bit will be deactivated. The syntax and description for these commands is given in Section 3.

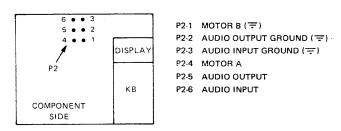

Figure 2-9 shows the location of the pins for audio in, audio out, and motor control.

Figure 2-9. ACI Connector Pins

# 2.7.1 RECORDER CONSIDERATIONS

In order to use the audio cassette efficiently several other aspects relevant to the recorder need further comment. These topics include:

- Cable hook up

- Volume and tone control positions

- Tape position

- Digital tape counter.

### CAUTION

The TM 990/189 audio cassette interface is not compatible with certain models of audio cassette decks. Reliable operation is only warranted with the following audio cassette models:

General Electric 3-5121B Panasonic RQ-413 AS Realistic CTR-40 Realistic CTR-41 Sears Model No. 799-21683700 Sharp RD610.

A Panasonic Model RQ-413AS tape recorder will be used for illustrative purposes. Table 2-3 provides a listing of the connections that are needed between the TM 990/189 and the recorder.

TABLE 2-3. RECORDER AND ACI CONNECTIONS

| Recorder        | P2 Connections                        |

|-----------------|---------------------------------------|

| Auxiliary Input | P2-5 (Audio Output) and P2-2 (Ground) |

| Earphone Output | P2-6 (Audio Input) and P2-3 (Ground)  |

The volume control should be set to approximately 80 percent of maximum and the tone control to mid-point.

The tape should be turned to the desired place on the tape where the recording is to be made and the initial value of the digital tape counter noted. After a "dump operation" is completed, the final reading of the digital tape counter should also be recorded. In this manner a number of programs may be stored and located on a single tape.

### 2.7.2 EXAMPLE OPERATION

This example will provide a step-by-step approach to using the audio cassette interface. It is assumed that the optional cassette control relay has not been installed.

### NOTE

If the relay circuitry is installed, a cable will be required between the remote input on the recorder to P2-4 (Motor A) and P2-1 (Motor B). This will allow the processor to start and stop the recorder. It should be noted at this time that this cable would have to be unplugged from the remote input for rewind operations.

### Procedure:

### Initial Set Up

- a. Make the necessary connections between the recorder and P2 as given in Table 2-3. Do not make any connections to the remote input on the recorder.

- b. Apply power to the TM 990/189 and the recorder.

- Enter the example program given in Section 3.3 into memory. Examine memory to

ensure that the program has been accurately entered.

- d. After inserting the cassette, position the tape to the desired starting place for the recording. If the desired starting place is the beginning of the tape, reset the digital tape counter to 000 prior to recording.

- e. Set the volume and tone controls to 80 percent and 50 percent respectively.

### 2. Dump Routine

The D command will be used to dump memory from the "start address" to the "stop address." The "entry address" is the address in memory where it is desired to begin program execution. In this case the proper syntax (See Section 3.3.6) for the D command is as follows:

$$D200 < T2 > 20\,E < T2 > 200 < T2 > IDT = EXAMPLE < T1 > READY? < Y >$$

After entering the D command, the monitor will respond with READY and wait for a Y (yes) keyboard entry indicating that the receiving device is ready. This allows the user to check recorder controls, tape position and the like before proceeding with the dump. If the recorder is set up correctly, press the RECORD button and then enter a Y on the keyboard to execute the D command. An appropriate time is allowed for the recorder to reach operating speed as indicated by a count down on the sound disc and LEDs CR0-CR3. In a similar fashion, the sound disc and the LEDs will signal when the dump has been completed.

If the user wants to expedite the dump sequence, two asterisks can be used following the IDT tag. Example: IDT = \*\*EXAMPL could be inserted in the syntax above to reduce dump time.

### 3. Load Routine

- a. In order to verify that the program can be properly loaded back into memory, change the contents of M.A. 0200 to 020E to zeros.

- b. Rewind the tape to the dump starting position as indicated by the digital tape counter in this case reading 000.

- c. Enter the L command on the TM 990/189 keyboard. CR6 (FWD LED) will light indicating that the processor is now ready for the recorder to be turned on.

- d. Depress the PLAY button on the recorder. The SHIFT LED will go on and off while data transfer is occurring. LEDs CR0-CR3 and the sound disc will signal the end of the load routine.

- e. When the FWD indicator extinguishes, stop the recorder.

### 4. Check Out Routine

- a. The display on the TM 990/189 should display the name identifying the program. In this case, EXAMPLE should be displayed.

- b. Use the M command to inspect memory locations M.A. 0200 to M.A. 020E and verify that the contents are correct.

- c. The program counter has been loaded with the starting address of the program: the program is now ready to be executed.

### **SECTION 3**

### **UNIBUG MONITOR**

### 3.1 GENERAL

A monitor is a program that implements the UNIBUG commands and subroutines. A command specifes the operation that is to be performed (example: Memory Inspect/Change). A subroutine is a program that carries out a specific task (example: typewriter program configures the TM 990/189 so that the keyboard acts as a typewriter keyboard). The monitor used in the TM 990/189 provides sixteen commands and seven subroutines.

The commands and subroutines available in the TM 990/189 reside in a TMS 4732 ROM (board socket U 33). This section provides a description of the commands and subroutines available in the monitor.

# 3.2 UNIBUG COMMANDS

The 16 UNIBUG commands are given in Table 3-1. The following paragraphs will give the syntax and description for each command along with examples involving most of the commands. Conventions used to define command syntax are listed in Table 3-2.

TABLE 3-1. UNIBUG COMMANDS

| Input | Results                                     | Paragraph |

|-------|---------------------------------------------|-----------|

| Α     | Assembler Execute                           | 3.3.3     |

| В     | Assembler Execute With Current Symbol Table | 3.3.4     |

| C     | CRU Inspect/Change                          | 3.3.5     |

| D     | Dump Memory to Cassette                     | 3.3.6     |

| E     | Execute to Breakpoint                       | 3.3.7     |

| F     | Status Register Inspect/Change              | 3.3.8     |

| j     | Jump to EPROM                               | 3.3.9     |

| ı     | Load Memory from Cassette                   | 3.3.10    |

| M     | Memory Inspect/Change                       | 3.3.2     |

| <br>Р | Program Counter Inspect/Change              | 3.3.11    |

| R     | Workspace Register Inspect/Change           | 3.3.12    |

| s     | Single Step                                 | 3.3.13    |

| т     | "Typewriter" Program                        | 3.3.1     |

| w     | Workspace Pointer Inspect/Change            | 3.3.14    |

| Ret   | New Line Request                            | 3.3.15    |

| S     | Terminal Load/Dump Option                   | 3.3.16    |

**TABLE 3-2. COMMAND SYNTAX CONVENTIONS**

| Convention<br>Symbol | Explanation                               |

|----------------------|-------------------------------------------|

| < >                  | Required items to be supplied by the user |

| [ ]                  | Optional items to be supplied by the user |

| (Ret)                | Return                                    |

| T1                   | Space                                     |

| T2                   | Space or comma                            |

| Т3                   | Space, comma, or return                   |

| LF                   | Line Feed                                 |

| R or Rn              | Register (n = $0$ to $15$ )               |

| WP                   | Current User Workspace Pointer contents   |

| PC                   | Current User Program Counter contents     |

| ST                   | Current User Status Register contents     |

# NOTE

Except where indicated otherwise, no space is necessary between the parts of these commands. All numeric input is assumed to be hexadecimal; the last four digits input will be the value used. Thus a mistaken numerical input can be corrected by merely making the last four digits the correct value. If fewer than four digits are input, they are right justified with leading zeros.

Prior to discussing the aforementioned commands, an example program will be given. The example program serves as an aid to developing an understanding of command operations.

# 3.3 PROGRAM EXAMPLE

### a. Problem:

XOP

1,13

0210

Write a program that will add  $33_{10}$  and  $15_{10}$  and display the answer.

| b. | Program S<br>LWPI | olution:<br>>0300   | Load immediate to workspace pointer.         |                                                                           |

|----|-------------------|---------------------|----------------------------------------------|---------------------------------------------------------------------------|

|    | LI<br>Li          | 0,33<br>1,15        |                                              | n first number (33 <sub>10</sub> )<br>n second number (15 <sub>10</sub> ) |

|    | A<br>XOP<br>XOP   | 1,0<br>0,10<br>1,13 | Add, answer<br>Display conto<br>Turn display |                                                                           |

| C. | Program<br>LWPI   | >300                | Address<br>0200<br>0202                      | Hex Contents<br>02E0<br>0300                                              |

|    | LI                | 0,33                | 0204                                         | 0200                                                                      |

|    | LI                | 1,15                | 0206<br>0208<br>020A                         | 0021<br>0201<br>000F                                                      |

|    | A                 | 1,0                 | 020C                                         | A001                                                                      |

|    | XOP               | 0,10                | 020E                                         | 2E80                                                                      |

2F41

- d. To enter the previous program:

- 1. Apply power to the TM 990/189

- The TM 990/189 will energize in a power up LOAD state and the display will show CPU READY.

| DISPLAY      | ENTER | COMMENTS                                          |

|--------------|-------|---------------------------------------------------|

| CPU READY_   | (Ret) |                                                   |

| ?_           | (Net/ | UNIBUG commands can be entered now                |

| ?M_          |       | Memory Inspect/Change                             |

| ?M 200_      | 200   | M.A. 0200                                         |

| 0200 = XXXX_ | (Ret) | Current Contents M.A. 0200                        |

| XXXX 02E0_   | 02E0  | Enter New Contents                                |

| 0202 = XXXX_ | (Sp)  | Advance to Next M.A. Current Contents M.A. 0202   |

| 0202 0300_   | 0300  | Enter New Contents                                |

|              | (Sp)  |                                                   |

| 0204 = XXXX_ | 0200  |                                                   |

| XXXX 0200    | (Sp)  |                                                   |

| 0206 = XXXX_ | 0021  |                                                   |

| XXXX 0021_   | (Sp)  |                                                   |

| 0208 = XXXX_ | 0201  |                                                   |

| XXXX 0201_   | (Sp)  |                                                   |

| 020A = XXXX_ | 000F  |                                                   |

| XXXX 000F_   |       |                                                   |

| 020C = XXXX_ | (Sp)  |                                                   |

| XXXX A001_   | A001  |                                                   |

| 020E = XXXX  | (Sp)  |                                                   |

| XXXX 2E80    | 2E80  |                                                   |

| 0210 = XXXX  | (Sp)  |                                                   |

| XXXX 2F41    | 2F41  | The entire program has been entered at this point |

e. Now that the example program has been entered, it will be examined for errors prior to executing it. To examine the previous program:

| DISPLAY    | ENTER | COMMENTS                                                                                                  |

|------------|-------|-----------------------------------------------------------------------------------------------------------|

| ?_         | (Ret) |                                                                                                           |

| :-<br>?M_  | M     | Memory Inspect/Change                                                                                     |

| ?M 200_    | 200   | Program Starting M.A.                                                                                     |

|            | (Ret) |                                                                                                           |

| 0200=02E0_ | (Sp)  | Data is Correct (DIC)                                                                                     |

| 0202=0300  | (Sp)  | DIC                                                                                                       |

| 0204=0200_ | (Sp)  | DIC                                                                                                       |

| 0206=0021_ | •     | DIC                                                                                                       |

| 0208=0201_ | (Sp)  | DIC                                                                                                       |

| 020A=000F_ | (Sp)  | DIC                                                                                                       |

| 020C=A001  | (Sp)  | DIC                                                                                                       |

| 020E=2E80  | (Sp)  | DIC                                                                                                       |

| 0210=2F41  | (Sp)  |                                                                                                           |

| UZ IU=2F41 |       | DIC  Note: If an error is found at any  M.A., simply enter the correct data and proceed to the next  M.A. |

Now that the sample program has been presented and the proper method for entering and examining a program given, the method for executing the previous program will be given.

- f. To execute the previous program:

- Set the program counter using the P command to the starting address of the program (0200 in this case).

- 2. Use the E command without breakpoint to execute the program.

| DISPLAY   | ENTER | COMMENTS                                |

|-----------|-------|-----------------------------------------|

| ?_        | (Ret) |                                         |

| P=XXXX    | Р     | Current PC value                        |

| XXXX 0200 | 0200  | Set PC to 0200                          |

| ?_        | (Ret) |                                         |

| ?E_       | E     |                                         |

| 0030_     | (Ret) | Execute program The answer is displayed |

# 3.3.1 TYPEWRITER PROGRAM (T)

Syntax

Т

### Description

Each time the T command is entered, a subroutine called the "Typewriter" program is called up. This program allows the user to use the keyboard as a typewriter and insert a string of characters in the display buffer. This program is quite useful in familiarizing the user with the characters produced at the display (see Table 2-1).

### **EXAMPLE:**

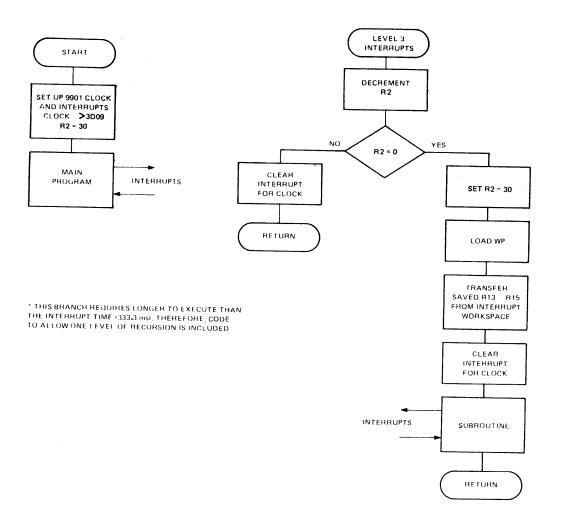

| DISPLAY    | ENTER  | COMMENTS                            |