# Micro-Professor MPF-I Student Work Book

MULTITECH INDUSTRIAL SORPORATION

Copyright © 1982 by Multitech Electronics Inc. and Multitech Industrial Corp.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher

#### MULTITECH INDUSTRIAL CORPORATION

OFFICE/ 977 MIN SHEN E. ROAD, TAIPEI, 105, TAIWAN, R.O.C. TEL:(02)769-1225(10 LINES)

TLX:23756 MULTIC, 19162 MULTIC.

FACTORY/5. TECHNOLOGY ROAD III, HSINCHU SCIENCE-BASED INDUSTRIAL PARK

HSINCHU, TAIWAN, 300, R.O.C. TEL:(035)775102(3 LINES)

#### Multitech Electronics Inc.

195 West El Camino Real Sunnyvale, CA. 94086 U.S.A.

Tel: 408-7738400 Tlx: 176004 MAC SUVL Fax: 408-7498032

# Micro-Professor<sup>™</sup> MPF-I Student Work Book

#### CHAPTER 1.

| 1 • 1                   | Unpacking and Installation4                                                   |

|-------------------------|-------------------------------------------------------------------------------|

| 1 • 2                   | Programming Languages5                                                        |

| 1 • 3                   | Testing & Familiarization                                                     |

| 1 • 4                   | Program in English6                                                           |

| 1 • 5                   | Program Explained6                                                            |

| 1 • 6                   | Assembly Listing 7                                                            |

| 1 • 7                   | Checking for Data Entry Errors 8                                              |

| 1 • 8                   | Program Execution9                                                            |

| 1 • 9                   | Checking the Results 9                                                        |

| CHAI                    | PTER 2.                                                                       |

| 2 • 1                   | Reset or Monitor: What's the Difference?13                                    |

| 2 • 2                   | Is the MPF-I a New Recording Artist?15                                        |

| 2 • 3                   | More Keys17                                                                   |

| 3 · 1<br>3 · 2<br>3 · 3 | PTER 3.  ASSEMBLYthe Sane Way to Go 21 Easier to Read 22 Easier to Program 23 |

| 3 • 4                   | Easier to Correct 23                                                          |

| 3 • 5                   | How to Proceed Using the MPF-I                                                |

| СНА                     | PTER 4.                                                                       |

| 4 • 1                   | Central Processing Unit (CPU)29                                               |

| 4 • 2                   | PIN-OUT30                                                                     |

| 4 • 3                   | Memory31                                                                      |

| 4 • 4                   | RAM32                                                                         |

| 4 • 5                   | Dynamic RAM, Static RAM33                                                     |

| 4 • 6                   | <b>ROM</b> 33                                                                 |

| 4 • 7                   | Monitor Program and ROM of the MPF-I34                                        |

| 4 · 8<br>4 · 9<br>4 · 10<br>4 · 11<br>4 · 12<br>4 · 13<br>4 · 14<br>4 · 15 | Address       35         Byte, Bit       36         Clock       37         Reset       38         Ports       38         Peripherals       38         Parallel I/O Lines       39         Advanced Hardware Description (Optional)       41 |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 • 16                                                                     | Power Supply 42                                                                                                                                                                                                                             |

| ĆHAP <sup>-</sup>                                                          |                                                                                                                                                                                                                                             |

| 5 • 1                                                                      | Learn by Doing                                                                                                                                                                                                                              |

| 5 • 2                                                                      | Flashing a Wessage                                                                                                                                                                                                                          |

| 5 • 3                                                                      | Program Analysis52                                                                                                                                                                                                                          |

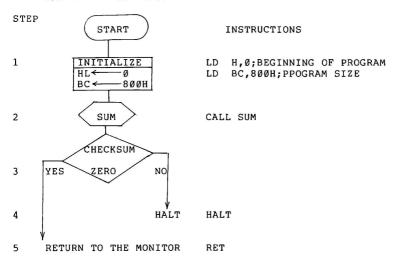

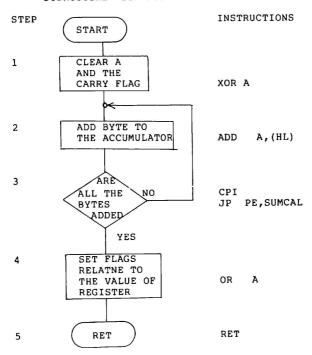

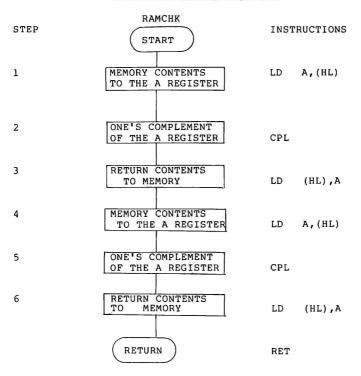

|                                                                            | Memory Checking72                                                                                                                                                                                                                           |

|                                                                            | EPROM Testing72                                                                                                                                                                                                                             |

|                                                                            | CPI77                                                                                                                                                                                                                                       |

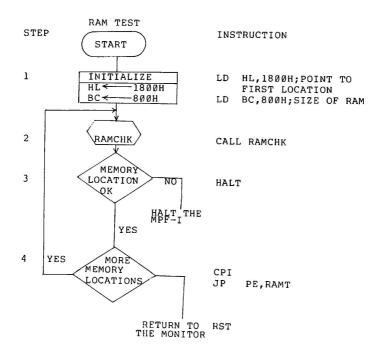

|                                                                            | RAM81                                                                                                                                                                                                                                       |

|                                                                            | Questions82                                                                                                                                                                                                                                 |

|                                                                            | Answers 90                                                                                                                                                                                                                                  |

| CHAP                                                                       |                                                                                                                                                                                                                                             |

| 6 • 1                                                                      | Exercises and Experiments 97                                                                                                                                                                                                                |

| 6 • 2                                                                      | Questions of Exercises                                                                                                                                                                                                                      |

| 6 • 3                                                                      | Answers to Exercises133                                                                                                                                                                                                                     |

| СНАР                                                                       | TER 7                                                                                                                                                                                                                                       |

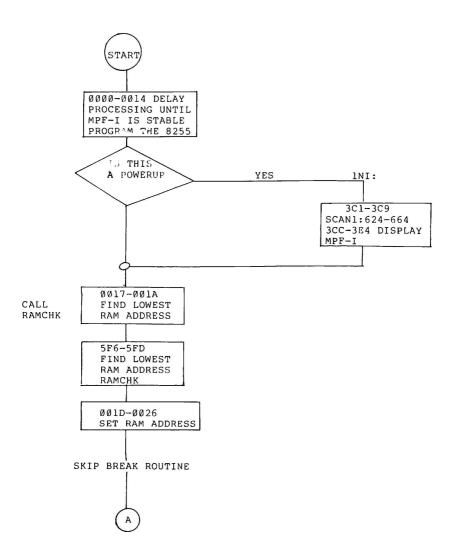

| 7 • 1                                                                      | Major Divisions of the Monitor                                                                                                                                                                                                              |

| 7 • 2                                                                      | The Code                                                                                                                                                                                                                                    |

|                                                                            | Answers to Exercises                                                                                                                                                                                                                        |

#### **CHAPTER 8**

| Sheet 1 of 4                            | 189 |

|-----------------------------------------|-----|

| Sheet 2The Control Function of the 8255 | 203 |

| Sheet 3Counter Timer Circuit (CTC) and  |     |

| Parallel I/O (PIO)                      | 264 |

| Sheet 4                                 | 204 |

|                                         |     |

|                                         |     |

#### **APPENDIX**

| Appendix        | Α | References ······                   | 2015 |

|-----------------|---|-------------------------------------|------|

| <b>Appendix</b> | В | Alphabetical Listing of Monitor and |      |

|                 |   | Interrupt Key                       |      |

| Appendix        | С |                                     | 210  |

# CHAPTER 1

This workbook is designed for the first time user of microprocessors and microcomputers but intends to explore the world of microcomputers. The workbook guides you step by step in your learning about microcomputers. We know that you will learn a great deal and also enjoy becoming familiar with microprocessors.

The fastest and most pleasant way to learn is to learn by doing. You are encouraged to use a MPF-I microcomputer to do the interesting experiments so that you can learn more quickly.

This workbook will first teach you to press a few keys on the MPF-I to see how it responds. And then, the workbook will teach you to press more keys and let the MPF-I show you the interesting results. As you progress in this workbook you learn new modes of operation. What is more important, you will eventually learn a great deal about microcomputers and microprocessors. To put it simply, you will know how to use computers to solve problems.

Never let a computer scare you! When automobile was first introduced to the world, few people were familiar with it. Even today, you don't have to know everything about an automobile to drive it. For example, you don't have to know too much about the complicated automobile transmission system to drive a car. But of course, you have to know some basic principles so that you can shift the gears properly. Operating a computer can be reduced to basic principles. Once these principles are learned, you can determine whether you want to continue and become a customer engineer (automechanic), an operator (a professional driver), or a designer (an automative engineer.)

To learn how to drive a car, you must become familiar with the features or functions of some devices or equipment such as the engine, steering wheel, etc. (In the realm of computer, these devices or equipment are generally referred to as "hardware".) You must at least know the names of some computer hardware devices and equipment and their basic functions. Once you have learnel to drive a car, your every move comes naturally and easily. The same is true about (operating) a computer.

The manuals that accompany your Microprofessor are designed for reference and to suggest experiments by showing examples. To get started, it is suggested that you follow the procedures given below.

#### **Exercises and Experiments.**

As you proceed through this workbook, you will see the notation Exercise 6-1, Exercise 6-2,..., in the This is a signal to proceed to the secleft margin. tion named EXERCISE and find the same number 6-1, 6-2,.... You should answer any questions in the exercise and then proceed to the ANSWER section to check your work. You will also be asked to perform experiments (answer questions) in the Experiment Manual (Hardware/Software). The answers to these questions are usually found in the section named EXPERIMENTS. sionally, an answer to an experiment will be part of an answer to an exercise.

#### 1 • 1 Unpacking and Installation

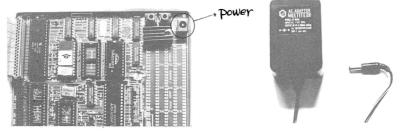

Open the "book" containing the Microprofessor (MPF-I). Locate the power connector in the upper right-hand corner. (Fig. 1-1)

Find the AC adaptor. The adaptor (Fig. 1-2) is a black box labeled "AC ADAPTOR MULTITECH". You should make certain that the voltage input shown on the adaptor matches the voltage supplied by your outlet. In the United States it is assumed (unless a special order is made) that the supply is 117 VAC - which is usually referred to as one-ten (110 V). You should also check the frequency; the label on the adaptor will show the frequency in hertz (Hz).

Plug the 9V circular shaft into the power receptacle on the MPF-I. The side opposite the AC adaptor label is to be plugged into your AC power outlet.

- \*\*\*\*\*\*\*\*\*\*\*\*\*\* \* CAUTION : DO NOT TOUCH THE PRONGS WHILE PLUGGING \*

- \* THE AC ADAPTOR INTO YOUR OUTLET!

#### 1 · 2 Programming Languages

What is a program? How can a program be run (executed)? To answer these questions, you should know how a computer communicates with the people who use it. A computer sometimes can be regarded as a loyal servant who always follows the instructions given by the master. Once the master has some good tasks for a computer to do or requires a computer system to solve some problems, the master gives step-by-step instructions to the computer. Each and every step that is required to solve a problem or to perform a task are given clearly to the computer. These instructions constitute a program. Any person who writes a computer program is called a programmer. In order to program, you have to learn computer programming languages such as ASSEMBLY, BASIC, PASCAL, APL, FORTRAN, and FORTH. We will discuss ASSEMBLY language in later chapters.

Now you know that a programmer can give instructions to a computer. How does a computer talk to a person? In the case of the MPF-I, a six digit LED (light emitting diode) display and a built-in speaker are used to tell a programmer what the MPF-I is doing. The MPF-I display can show modified Roman letters and Arabic numerals from 0 to 9 plus some special signs.

#### 1 · 3 Testing & Familiarization

In the exercise below, you will be shown how to enter and execute a short program. Performing this exercise will test some of the MPF-I functions and familiarize you with the MPF-I's Z80 microprocessor. The program used in this chapter adds two numbers, and stores the result in memory.

#### 1 · 4 Program in English

Load the first number (5) into the A register, and the second number (4) into the B register. Add the content of the B register (4) to the content of the A register (5), and put the result (9) in the A register. Then, store the value of the A register in memory location 1830H (H stands for hexadecimal) and finally halt the Microprofessor.

If you are already familiar with registers and ASSEMBLY language programming, you may want to skip the next section, although it is highly recommended for anyone.

#### 1 • 5 Program Explained

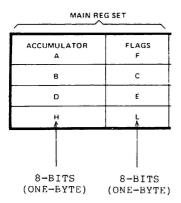

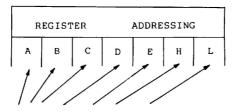

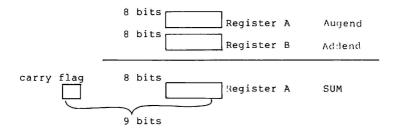

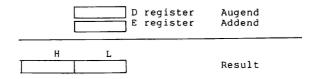

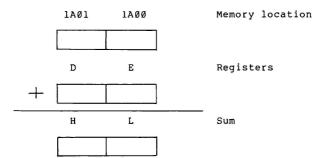

In the program, you will instruct the MPF-I to access the A register and load it with a value: (5). Now you may ask: "What is a register?" A register is an area in the CPU that stores different kinds of information. It can be regarded as a memory and a work area. Generally, the registers of Z80 CPU are divided into two categories—general purpose registers and special purpose registers. The general purpose registers are named A, B, C, D, E, F, H, and L. The special purpose registers include PC, SP, IX, IY, I and R. In the case of our program, 5 is placed in the A (accumulator) register. Because the A register must contain one of the values in any 8-bit arithmetic operations. It is, therefore, often called the Accumulator. When 5 has been loaded into A, 4 will then be loaded into B register. The values in the A and B registers will be added together and placed into the A register. The value in the A register will be stored at memory location 1830H, then the MPF-I will be halted.

#### 1 · 6 Assembly Listing

All of the program is entered into the MPF-I in hexadecimal (hereafter, we will use the common abbreviation hex for hexadecimal.) Therefore, you first write your program in Assembly language and then translate it into hexadecimal. Most of the demonstration programs written in MPF-I manuals will also be listed in machine language code which is in hexadecimal. A complete Assembly program listing is shown below.

| 1800 | 3EØ5   | LD   | A, 5  |   |

|------|--------|------|-------|---|

| 1802 | 0604   | LD   | B, 4  |   |

| 1804 | 80     | ADD  | A, B  |   |

| 1805 | 323018 | LD   | 1830, | Α |

| 1808 | 76     | HALT |       |   |

|      |        |      |       |   |

You will now enter the object (machine) language code shown in the Assembly, program listing. If you haven't already done so, connect your MPF-I to the power source. Now press the system reset key  $\overline{\rm RS}$  (the  $\overline{\rm RS}$  key is used for initializing the MPF-I). Since the memory locations at which you can store programs begin at hexadecimal location 1800H, entry of object code will start at 1800H. Press the address key  $\overline{\rm ADDR}$ . A random address will be displayed on the four leftmost digits; these digits will be referred to as the address field.

Enter the starting address for the machine language code by pressing  $\boxed{1}$ ,  $\boxed{8}$ ,  $\boxed{0}$ ,  $\boxed{0}$ . The same result can be obtained by pressing the program counter  $\boxed{PC}$  key (this only works when your program starts at 1800H). Now inform the Micro-Professor that data is to be entered by pressing  $\boxed{DATA}$ . Refer to line 2 of the assembly program listing. Line 2 contains two bytes of object code 3E and 05.

Key in the first byte by pressing  $\ensuremath{\mbox{3}}$  and then  $\ensuremath{\mbox{E}}$  . The display should now show:

Advance the address field display by pressing + . The display will show:

Enter the second byte of hexadecimal data by pressing 0 and then 5 . The display should be:

Line 3 of the listing also contains two bytes of hexadecimal data; enter these bytes by keying:

In a similar manner, enter the rest of the program, namely:

#### 1 • 7 Checking for Data Entry Errors

The program has been entered. It is wise to check for entry errors. Press  $\overline{\text{ADDR}}$ ,  $\overline{1}$ ,  $\overline{8}$ ,  $\overline{\emptyset}$ ,  $\overline{\emptyset}$ . Are the rightmost two digits in the data field equal to 3E? If not, press  $\overline{\text{DATA}}$  and enter  $\overline{3}$ ,  $\overline{\mathbb{E}}$ . To examine the next byte press  $\overline{+}$ . Is there a 05 in the data field? If the display is correct continue inspection of all the remaining data using the  $\overline{+}$  key. If the present byte or any successive bytes are incorrect, enter the correct data.

#### 1 · 8 Program Execution

There are two ways to begin execution at address 1800H. The simplest is to press  $\overline{RS}$ ,  $\overline{PC}$  and then  $\overline{GO}$ . (The  $\overline{PC}$  and  $\overline{GO}$  keys are used in program execution.  $\overline{PC}$  stands for program counter. This key is used to tell the MPF-I where a program begins. The  $\overline{GO}$  key is a signal (that says: "You may go execute the program".) The second method allows execution to begin at any address.  $\overline{PRS}$ ,  $\overline{ADDR}$ , the beginning execution address e.g. 1 , 8 , 0 , 0 , then press  $\overline{GO}$ . When you press  $\overline{GO}$  (in the above program), the screen will go blank and stay blank. The program has reached the HALT instruction and is waiting for the next operator action.

#### 1 · 9 Checking the Results

To regain control of the keyboard functions, press MONI. The answer to 5+4 was stored at location 1830H. Key in  $\boxed{\text{ADDR}}$ ,  $\boxed{1}$ ,  $\boxed{8}$ ,  $\boxed{3}$ ,  $\boxed{\emptyset}$ . The display should show:

Now let's check what was stored in the registers. Press the (REG) key. The word REG should show on the display.

Press AF; this will display the contents of the AF register pair. The first two digits contain the contents of A register, and the middle 2 digits display the contents of F register. Do not worry about the F register now. We are only concerned with the value in A register. Didn't we store a five in A register? And then, didn't we add the contents of B register (4) to the contents of A register? If A register contains a nine, then it is correct. Press REG then the BC key. In this case we are looking at the contents of the BC register pair. Are the numbers in the leftmost 2 digits 04? If they are, then Congratulations! You have just successfully entered your first object code program onto the MPF-I. If something went wrong, you may find the answer to your problem in the next section.

When you made the following errors:

- l) A byte was incorrectly entered. Write the correct byte over the incorrect byte.

- 2) One or more bytes were left out. Read section 3.3.3 (in the User's Manual), then remove the bytes one by one.

- 3) One or more bytes need to be added. Read section 3.3.2 (in the User's Manual), then add each byte.

## CHAPTER 2

Are you Keybored? O.K. Now you know how to enter a program and, so far, your experience with running a program has been successful. But if you're like us, you may be KEYBORED!

Some symptoms of this disease are confusion with each key functions, and adversion to abbreviations such as  $\overline{\text{ADDR}}$ ,  $\overline{\text{REG}}$ ,  $\overline{\text{SBR}}$  and  $\overline{\text{INS}}$ , and finally, allergic reactions to white, grey and orange rectangles. The good news is that this disease is painlessly curable, our RX: read this chapter and find out how to avoid entering the same program over and over.

#### 2 · 1 Reset or Monitor: What's the Difference?

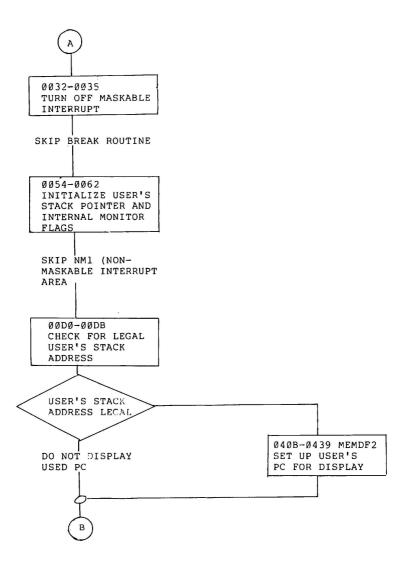

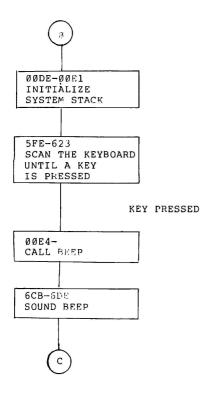

In chapter 1, you entered a program, and you were told there were two ways to stop the execution of a program. One was to press the MONI key, in which case the display shows a memory address, or you could press the RS key, in which case the display will show MPF-I. If you were sharp, you might have noticed that we didn't press the RS key to stop the program when we were planning to look at the contents of the registers. This is because of the RS key is used: (1) to perform a hardware reset of the CPU, (2) to initialize the monitor program, and (3) to transfer control to the monitor.

If we were to initialize the monitor program before we went to check the values in a register, those values might not remain the same. Unlike the  $\overline{\text{RS}}$  key, the  $\overline{\text{MONI}}$  key transfers control immediately to the monitor. The address at which the program was currently at when the  $\overline{\text{MONI}}$  key was pressed is displayed along with the data at that location. Enter the following program, and we'll do a short experiment with the  $\overline{\text{MONI}}$  and  $\overline{\text{RS}}$  keys.

|               |        | 1;p | olice | car | sirer          | 1:      |   |

|---------------|--------|-----|-------|-----|----------------|---------|---|

| 1800          |        | 2   |       | ORG |                | 1800H   |   |

| 1800          | ØEØØ   | 3   | LOOP  | LD  |                | C,Ø     |   |

| 1802          | 210000 | 4   |       | LD  |                | HL, ØCØ | Н |

| 1805          | CDE405 | 5   |       | CAL | Ĺ              | TONE    |   |

| 1808          | ØECØ   | 6   |       | LD  |                | C,ØCØH  |   |

| 18 <b>0</b> A | 210001 | 7   |       | LD  |                | HL,100  | Н |

| 18ØD          | CDE405 | 8   |       | CAL | L <sub>1</sub> | TONE    |   |

| 1810          | 18EE   | 9   |       | JR  |                | LOOP    |   |

|               |        | 10  |       | ;   |                |         |   |

|               |        | 11  | TONE  | EQU |                | Ø5E4    |   |

|               |        | 12  |       | END |                |         |   |

If you had any problems entering the above program, you need to review chapter 1.

Now for the experiment, after you have loaded the program, press  $\overline{PC}$ , then  $\overline{GO}$ . If everything was entered correctly, you should hear a sound similar to a European police car siren. Now, to stop the execution, press  $\overline{RS}$ . What happens?  $\overline{LVF-I}$  appears on the display. Begin the program again and this time, stop it with  $\overline{MONI}$ . What happens this time? Instead of going back to ground zero and initalizing the system,  $\overline{MONI}$  simply halted the program

where it was and allowed you to examine the registers. When the program is halted the left 4 display digits show the program counter (where the program was halted) and the 2 right display digits show the opcode at the halted address. Press  $\boxed{\text{GQ}}$  and  $\boxed{\text{MONI}}$  several times and notice that the contents of the PC counter address will vary.

#### 2.2 Is the MPF-I a new recording artist?

But the MPF-I does make tapes. Well, not exactly. Examine the top, righthand corner of your MPF-I. Next the power socket, you will find two circular metal jacks. When a cassette recorder cable is connected to these sockets and to a recorder, a simple storage of data can be Assuming you have the reguired cable and performed. recorder, let's make a tape of the police siren program you have use just entered. You may wish to check to see if the siren program is still in the MPF-I memory. If not, reenter the program. Connect the cables from the cassette recorder Make sure to connect the cable from the EAR to your MPF-I. jack to the MPF-I's EAR socket. Do the same with the MIC cable and socket. Now, press on the TAPE WR key. screen will show a random number in the address field. display should be similar to this:

#### x.x.x. -F

The -F in the data field is the mnemonic for (stands for) filename. The filename is used to distinguish different data sets stored on a single cassette. It is also used to read back data. You can use any combination of the 16 lettered and numbered keys in the filename. For your first try, let's use something easy to remember, e.g. 0001. Enter [0,0,0,1. Now enter + to move on to the next display. You will again see a random number in the address field and the display should look like this:

#### x.x.x.x. -S

Now let's read the data we wrote to tape back into the MPF-I. Press TAPE RD. We now have that familiar mnemonic (-S) on the screen again. Input 0001, or whatever filename you used in the above exercise. Rewind the cassette and press GO on the MPF-I. Press PLAY on the recorder. The screen will go blank, periods will be displayed for a few moments, now the filename of the program at that location will be displayed. In this case 0001, the program will now be read in. When the "noise" stops, stop the recorder and reset the MPF-I. Now press FC and GO. Is the program the same? If so, congratulations! If not repeat the above process with a different volume setting.

#### 2 · 3 More Keys

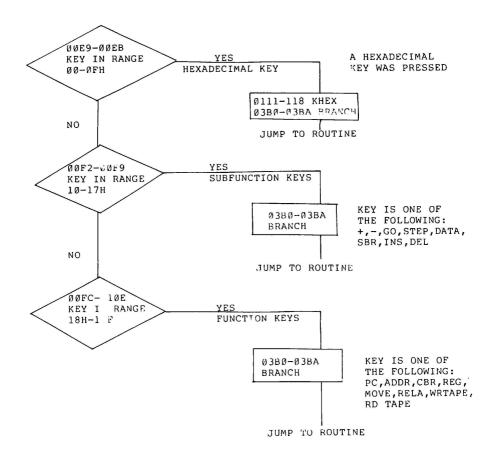

The MPF-I allows users a great deal of flexibility and power through keyboard entries. How does a user become familiar with the keyboard functions? An appendix with an alphabetic listing of the keys is at the back of this manual. But, do you really need to read about each key? I recommend you proceed through the manual and learn how to use the keys in the context of programming. Use the appendix for reference.

#### **Keyboard Familiarization Questions**

- 1. Which keys do not cause a tone to sound when pressed?

- 2. Why is the RESET key the only key that is brightly colored?

- 3. Look at the MPF-I User's Manual, Table of Contents-3, Operation introduction. Two of the gray keys are not listed -- which ones?

- 4. Can you press any key that would cause damage to the MPF-I?

- 5. There is a magic key that will tell the Micro-Professor I to do exactly what you want done. What is this key?

#### **Keyboard Familiarization Answers**

- 1. RESET, MONI, INTR, USER KEY.

- This key is the MPF-I PANIC button. The color should also serve as a warning that the current contents of the registers will be lost, when RESET is pressed.

- 3. INTR and USER KEY. Additional programming must be done to make these keys perform a function.

- No, not unless you hit the key with a hammer. Pressing the wrong key can change your program.

- 5. GO. If a program has been entered and it is correct.

### CHAPTER 3

Keeping Your Sanity— (or How not to Write in Object Code)

#### 3 · 1 ASSEMBLY--the Sane Way to Go

In earlier chapters there have been hints that you should first write your program in Assembly Language. The major reasons for Assembly programming are:

- Easier to readEasier to write programsEasier to correct errors

#### 3 · 2 Easier to Read

What does the 3 instruction program below do?

0011 1010 0000 0000 0001 1010 1100 0110 0000 1000 0011 0010 0000 0010 0001 1010

After looking at the binary code you probably don't care. OK! Here is the same program in hexadecimal.

3A ØØ 1A C6 Ø8 32 Ø2 1A

How can the hexadecimal program be decoded? Open the MPF-I User's Manual to Appendix C. Find the section Z80-CPU INSTRUCTIONS SORTED BY OP-CODE. Search for the opcode 3A (Second column almost halfway down). The row reads

3A 8405 LD A, (NN)

OH! LD stands for load.

A load means making a copy of the data, usually one or two bytes, then entering the data into a stated destination. In this instruction, a byte is loaded from memory into A register. The form LD A,(NN) is still a little hard to read. The Assembly language instruction is

LD A, (1AØØH)

which means :

- (1) find memory location 1A00 (hexadecimal),

- (2) make a copy of the byte at location 1A00,

- (3) then replace contents of the A register with the copy from memory.

The entire program is

LD A, (1AØØH) ; A <— (1AØØH)ADD A,8 ; A <— A + 8 LD (1AØ2H),A ; (1AØ2H) <— A

This program:

- 1) loads a value from memory into A,

- 2) adds 8 to the contents of A,

- puts the result (A register) in memory location 1A02H. Read the binary code again and compare with the Assembly language program.

#### 3 · 3 Easier to Program

In your program a test is to be made. If the value in the A register is zero, then a routine which clears the account book is to be executed. If the value of A is negative, then an overdraw routine is executed. Using Assembly language you can write:

```

JP Z,CLRACC ; If A=0 jump to clear account

JP M,OVERDR ; If A is minus (negative) jump

to overdrawn.

```

In object code programming (hexadecimal or binary) you may not know where the routines CLRACC and OVERDR will be in memory. This means you will have to leave a blank area in the code. Too many blank areas lead to the inability of locating the exact address where the jump was to be made to. In assembly language programming you just write the name of the routine e.g. CLRACE.

#### 3 · 4 Easier to Correct

Sooner or later it will become necessary to alter codes.-insert, delete, or add instructions. In Assembly language programming, you can usually find the code to be modified swiftly. To add a new line, simply write the instruction in mnemonic form.

#### 3.5 How to Proceed Using the MPF-I

- Decide what the program must do. Base your decisions upon the required input and output.

- Decide if you can write the program. You might be asked to compute an advanced mathematical function of which you have no knowledge.

- Decide whether the MPF-I can program the task. Unless a special interface is designed; electrocardiograms can't be read directly.

- Organize the program flow. Sometimes a flowchart helps.

- 5. Write the program in Assembly Language.

- Hand translate the program into object (hexadecimal) code.

- 7. Enter the hexadecimal code into the MPF-I's memory.

- Test the program.

- Make corrections in Assembly language and translate into object code.

- 10. Save the working program on tape.

#### **QUESTIONS**

1. Turn to Appendix C in the MPF-I USER's MANUAL. Find the section Z8Ø-CPU INSTRUCTIONS SORTED BY MNEMONIC. The table should begin with:

| OBJ  | SOURCE     |

|------|------------|

| CODE | STATEMENT  |

| 8 E  | ADC A,(HL) |

Use the table in the manual to fill in the missing entries in the table below.

| OBJ<br>CODE |     | CE<br>EMENT<br>A,(HL) |

|-------------|-----|-----------------------|

|             | CCF |                       |

|             | NEG |                       |

|             | LD  | (DE),A                |

|             | XOR | N                     |

|             | віт | 3,Н                   |

| <b></b>     | SRA | Α                     |

|             |     |                       |

2. In this section you will be asked to translate from object code (written in hexadecimal) to source code (written in assembly language). This is usually done when you can't read the source statement or are given some code in hexadecimal (this is a rotten situation).

Turn to Appendix C in the MPF-I User's Manual. Find the section Z80-CPU INSTRUCTIONS SORTED BY OP-CODE. The table should begin

| OBJ  | SOURCE    |

|------|-----------|

| CODE | STATEMENT |

| ØØ   | NOP       |

Use the table in Appendix C to fill in the entries in the table below:

| OBJ<br>CODE | SOURCE<br>STATEMENT |

|-------------|---------------------|

| 70          | LO (H L), B         |

| FF          | RST 38              |

| 00          | NOP                 |

| 50          | LD D. B             |

| A6          | LD D, B<br>AND (HL) |

| CB 10       |                     |

| DD CBO5CE   |                     |

| ED BO       |                     |

| FD 23       |                     |

Until you looked for CB, all you had to do is to find the object code is to go down a list in hexadecimal order –  $\emptyset$ , 1,2,3,4,5,6,7,8,9,A,B,C,D,E,F. All instructions starting with CB,DD,ED, and FD are in separate lists. The reason for the separate lists is that the Z8 $\emptyset$  executes these instructions differently. In a later chapter, some of these instructions will be explained.

#### **ANSWERS**

| SOURCE<br>STATEMENT |

|---------------------|

| ADC A,HL            |

| NEG                 |

| LD (DE),A           |

| BIT 3,H<br>SRA A    |

|                     |

| 2. | OBJ       | SOURCE       |

|----|-----------|--------------|

|    | CODE      | STATEMENT    |

|    |           |              |

|    | 7ø        | LD (HL), B   |

|    | FF        | RST 38H      |

|    | ØØ        | NOP          |

|    | 50        | LD D,B       |

|    | A6        | AND (HL)     |

|    | CB 10     | RL B         |

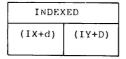

|    | DD CBO5CE | SET 1,(IX+D) |

|    | ED BO     | LDIR         |

|    | FD 23     | INC IY       |

|    |           |              |

## CHAPTER 4

This chapter will introduce to you some of the basic components (by basic, we mean they are indespensable.) and their functions.

Computers have been called "electronic brains" because computers can perform such operations as logic comparisons, arithmetic calculations, and more recently reasoning. But computers are much more than an electronic brain. Computer have become more like an individual human being. This will be discussed later.

#### 4 • 1 Central Processing Unit (CPU)

The "brain" of a computer or a microcomputer is its central processing unit (CPU). You may wish to know what a CPU looks like. The MPF-I has a Z80 microprocessor which is used as a CPU.

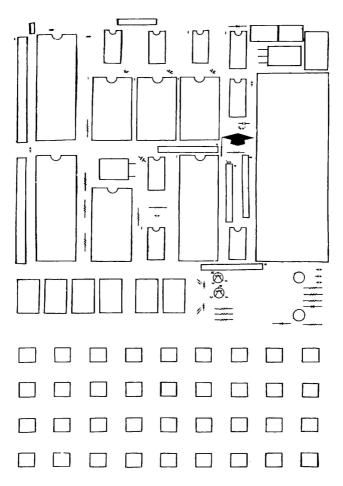

You can locate the Z80 CPU of MPF-I in a diagram on page 4 in the MPF-I User's Manual. At the upper left corner of the diagram, there is an rectangular area marked with Z80 CPU. Here is where the CPU is located.

You may have noticed that there is a notch on the upper edge of the Z80 CPÜ. The notch is used to indicate whether the Z80 CPÜ is inserted correctly into the socket. If the notch points upwards, the Z80 is correctly inserted. Otherwise, the Z80 CPÜ is not adaquately inserted and the MPF-I would run into trouble. Typically, reverse insertion causes the Z80 to overheat until it burns up.

Why does the Z80 CPU have to be mounted correctly? To answer the question, let's take a look at the CPU. The CPU is an n integrated circuit (IC) chip which is a 'tiny piece of silicon on which many microscopic circuits are built. The chip is packaged in two pieces of a Dual-In-Line package (DIPs) that keeps moisture, dust, and impurities away from the chip. But since the chip is sealed in the DIP package, the circuits inside the package need to be connected to outside circuits through pins as shown in the diagram on page C-l in the Appendix C of the MPF-I User's Manual.

#### 4 · 2 PIN-OUT

To make sure that a circuit inside the package is connected to a circuit outside of the package collectly, a specific pin is assigned to make a correct connection. As a result, each pin is given a specific pin number.

The diagram on page C-1 shows how pin numbers are assigned to pins. If an IC chip is inserted in reverse (that means the notch of the chip points downwards.), it results in incorrect connections of circuits. The pins are not numbered sequentially (1,2,3,4,...) but rather by function. For example the transfer of data in and out of the Z80 CPU is accomplished thru 8 data pins (14, 15, 12, 8, 7, 9, 10, 13). These 8 pins are grouped together and called the data bus.

There are several reasons for selecting Z80 as the CPU for the MPF-I. First, Z80 is one of the most popular microprocessors. It is used as the CPU of many microcomputers. Many software programs have been written to run on Z80 based computers. You can share or exchange software programs with others. Secondly, the Z80 instruction set was designed as an extention of instruction set for the Intel 8080 microprocessor. Therefore, almost any program written for an microprocessor can be executed on a Z80 microprocessor without any changes. The 8080 microprocessor is a very important microprocessor chip, for which many software programs already exist. Thirdly, the Z80 microprocessor (Z8Ø CPU) features two sets of general-purpose registers and additional special purpose registers which make it easier for computer users or programmers to write programs for 280 based microcomputers.

#### 4 · 3 Memory

Before we proceed to show how a CPU interacts with other devices, let's take a look at one of the major parts that constitutes a computer--memory. A human being must have a memory so that he or she can learn and think. A computer must have a memory in order to process information and solve problems.

Memory is generally defined as any device that can store data in such a manner that the information can be accessed (or reached) and retrieved (or fetched). In today's computers, the memories usually come in the form of IC chips. The appearance of these chips look similar to that of a CPU such as the Z80 microprocessor. They have DIP packages and pins. Each chip is assigned a specific number. This number indicates the functions the chip can perform.

#### 4 . 4 RAM

Now open the cover of your MPF-I, there is a 24-pin IC chip on the upper right part of your MPF-I. On page I-4 of your manual the chip is labeled RAM. The chip which is marked with either 2016, 58725, or 6116P-4, is a 16K static random access memory (RAM). On the part of the printed circuit board just above the IC memory chip, the words "U8" is marked to identify the location where the chip should be installed.

When you try to decipher the words "RAM" and "static" you may become frustrated. These words are just used to distinguish different types of memory chips. The most commonly used types of memory are RAMs, ROMs (read only memory), and EPROMs (erasable programmable read only memory).

The RAM, more correctly speaking, should be referred to as read/write memory. A more correct definition of RAM is random read/write memory. The RAM is a semiconductor memory into which information (data) can be stored (written) and retrieved (read out) again. RAMs differ from ROMs—once the power supply of a computer is turned off, the contents of a RAM disappear. As a result, RAMs are suitable for storing data which are to be used temporarily by a computer such as programs and data.

#### 4 • 5 Dynamic RAM, Static RAM

The RAM can be further divided into two types--static RAM and dynamic RAM. The static RAM is what is generally referred as those RAMs whose contents disappear, will only change, when written into or as soon as the power supply is turned off. The dynamic RAMs, even when power is continuously supplied can lose data if the contents of such RAMs do not go through a memory refresh process. Unlike some (many) CPUs the 280 provides a refresh signal.

#### 4 · 6 ROM

Data is read from a ROM. No data can be written into ROM chips. Even when the power supply is cut off, the contents of ROMs do not change. ROM chips are suitable for storing data that is to be used repeatedly.

#### 4 • 7 Monitor Program and ROM of the MPF-I

The location indicated by U6 is used to put a ROM for storing monitor programs. Almost every microcomputer uses a ROM or an EPROM memory chip for storing monitor programs, which are used to control the internal operations of a microcomputer. An EPROM is a close relative of the ROM. By applying ultraviolet rays an EPROM can be erased. Typical functions of a monitor program include the initialization of the CPU, keyboard scanning, display control, and responding to the function to be performed each time a key on the keyboard is pressed. In short, once a microcomputer is turned on, the CPU of the microcomputer begins to execute a monitor program. At location U6 in the MPF-I, either 16K PROMs such as 2716 and 2516 or 32K PROMs such as 2732 and 2532 can be used for storing monitor programs.

We have talked about the CPU, memory, and data input device (such as the MPF-I keyboard), and data output device (the display and speaker). Most of today's microcomputers have these four major components.

#### 4 · 8 Address

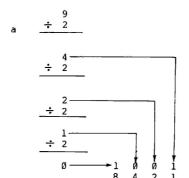

Just by watching the keyboard, you may guess that a programmer can key in a character like "A" or "7". But where can a character like "A" be stored in the MPF-I. How is it stored? A computer is designed so that it only recognizes "0"s and "1"s no matter who the manufactuer is. As a result, when you press a key to store a word, the computer first encodes the word into the series such as 01101001 and then stores the string of 0's and 1's into a specific location. Since the computer memory stores vast amounts of data, data should be stored or retrieved from specific locations to avoid confusion in data manipulation. Therefore, an "address" is given to identify the location of a specific item of data the same way as a specific building is assigned an address so that mail addressed to the building can be delivered properly.

#### ADDRESS BUS

The Z80 microprocessor uses 16-digit binary numbers to identify the locations of data stored in the memory devices that are connected to it. When the CPU of a computer intends to access the data stored in its memory devices, it communicates with its memory through a 16-line address bus. Each line of the address bus corresponds to a binary digit of the 16-digit address. And each line of the address bus can convey two signals to the memory--"0" and "1". Using 0 and 1, you can construct 65,536 16-digit numbers. That means the Z80 CPU can access up to 65,536 memory locations. The number 65,536 is often written 64K.

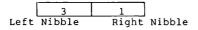

#### 4 · 9 Byte, Bit

We have mentioned that data is stored in the form of strings of 0's and 1's in a computer. In computer systems, memory size is measured in bytes. In Z80 based microcomputers such as MPF-I, a byte is equal to eight binary digits, e.g. 1. A byte looks like 00000000, llllllll, ll000101, or 01lll001. A byte is made up of eight "bits". In a binary numerical system, a bit is either a "0" or a "1".

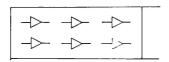

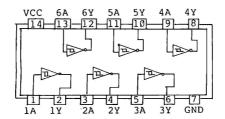

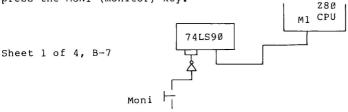

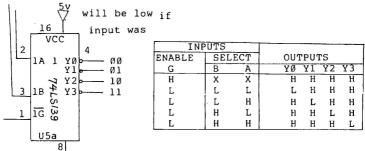

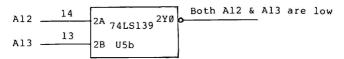

You may wonder how an item of information or data is accessed (for example from the keyboard). Turn to page I-B-3 (sheet 2 of 4). This schematic shows how the IC (8255) controls the input and output of data of the MPF-I. If you have not worked with hardware, do not expect to understand the details of how the 8255 controls devices such as the displays. Later in the workbook a detailed explanation will be given of the schematics. This chip controls MPF-I's data input and output devices such as LED displays, the keyboard, the cassette interface, the interface to MPF-I's CPU, and the address decoder. In the lower left part of the schematic (A, 7 and 8), you will find a chip (74LS139) which is connected to a pin of the 8225 chip marked CS (which stands for chip select). The 74LS139 is an address decoder used for deciding what range of memory addresses is being accessed by the CPU. There is a "--" on top of the mark CS. That means the address decoder works when the input of CS is low. A low means the voltage is pretty close to zero - probably 0.4 volts. We say the address decoder works is active low, because when the input of CS is low it becomes active.

# 4 • 10 Clock

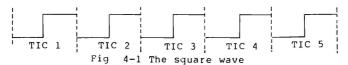

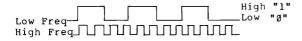

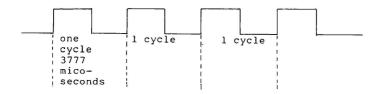

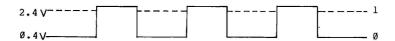

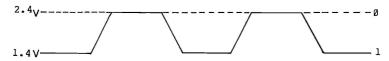

Chips (or large-scale integrated circuits, LSIs) in the Z80 family require a clock. The clock supplies a square wave of a certain frequency used for controlling transfer of data in the CPU. Every time the clock ticks, data is tansferred. The illustration below shows how a square wave looks like.

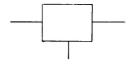

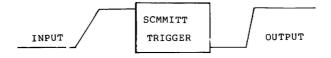

Chips using a clock have specific requirements for the High and Low voltages. A good source for a clock is a crystal oscillator. On a schematic, it looks like fig. 4-2.

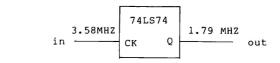

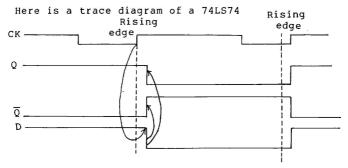

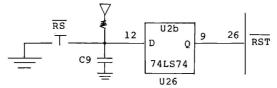

On sheet 1 of 4 of the MPF-I schematic, you can locate the crystal oscillator at (D-7) and (D-8).

The output of the crystal oscillator is connected to pin 3 of the IC 74LS74 (coordinates D-6), and then to pin 6 of the Z80 CPU (D-5). The standard designation for a clock is  $\overline{\Phi}$ . The label  $\overline{\Phi}$  is the point where clock signals go into the CPU.

#### 4 · 11 Reset

A requirement for a circuit to work properly is that it always starts the same way each time it is put to work. The Z80 CPU always starts (comes up) by addressing location 0000 when power is supplied and a pin called RESET is held low for a few cycles. Any time your MPF-I appears to be out of control, you may activate a circuit that resets the CPU. Pressing the RS button controls the circuit that supplies a reset signal to the Z80 CPU.

#### 4 · 12 Ports

Now we will take a closer look at the schematic for MPF-I input and output (sheet 2 of 4). On the right side of the 8255, there are three "ports". You may ask how ports can be built on a tiny 40-pin chip.

The word port conventionally means a harbor, a sea port where ships can sail in or out, loading or discharging large amounts of goods. In our study of microprocessors, a port can be regarded as a place where data from outside can be "loaded" into the CPU and where a CPU can "discharge" the data it has processed.

#### 4 • 13 Peripherals

The chip 8255 is a 40-pin programmable peripheral interface IC. Peripherals are generally referred to as those devices which interact with the CPU for certain purposes. If you use a cassette tape recorder to record data or programs, then we say the cassette tape recorder is a peripheral of the MPF-I. Peripherals can be a printer, auxiliary memory storage equipment, or a display terminal, etc.

#### 4 · 14 Parallel I/O Lines

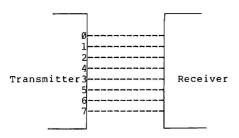

Of the 8255's 40 pins, there are 24 pins used as parallel input/output lines (we will use I/O instead of input/out hereafter.) The word parallel may puzzle you.

When data is transferred bit by bit, we generally call this method a serial data transfer. Data is transferred over telephone lines serially. If you want to input or output eight bits of data or several batches of data all at once, you have to use parallel I/O lines. In computer systems, data is usually transferred byte by byte between the CPU and ROM or RAM chips. As a consequence, we have to use parallel lines to connect the CPU and its memory devices. If a byte--01001001--is fetched by the CPU from its memory, each bit of this byte will be carried by a single parallel line to the CPU. Therefore, a data bus consisting of eight parallel bi-directional lines is used to supply data between the CPU, memory, and I/O ports.

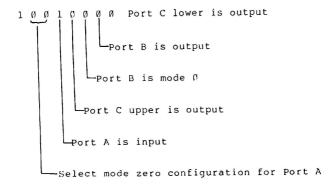

The 24 parallel I/O lines of the 8255 are divided into three ports—Port A, Port B, and Port C—with each port having eight parallel I/O lines. Each of the three ports is called an 8-bit port. Port A is an input port, because this port is used for collecting data (which will then be transferred) to the CPU. Port B and C are output ports, because the two ports are used for activating displays and keys.

You can locate Port A on the schematic sheet 2 of 4. In the lower right part of the IC 8255, there are eight pins marked with PAØ, PAI, PA2,...PA7. They are connected to eight parallel lines. Pin 37 (the pin marked PA7) is used for inputing data stored on cassette tape into the MPF-I. Pin 38 (the pin marked with PA6) is connected to the User key, which will become active when the signal on it is low. PAØ through PA5 are connected to six rows of the keyboard matrix. The input signal becomes low only when keys in the active column are pressed. Since the 8255 is programmable, a programmer can program a port to be input or output.

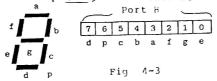

In the MPF-I, Port B is an output port used for controlling the LED displays. As you can see on the schematic, PB0 through PB7 is wired to the displays with eight parallel lines. Each pin or bit of Port B is used to control one of the seven segments of the LED display and the decimal point. Fig. 4-3 shows the name of each segment and the corresponding bit in Port B.

Port C has many functions. Bit 7 of Port C (PC7) is used for writing data into cassette tape. It is also connected to the speaker and an tiny LED lamp. Once you press a key on the keyboard of the MPF-I, the speaker of the MPF-I will generate a sound and the LED lamp will blink. Except for the keys marked with  $\overline{\text{RS}}$ ,  $\overline{\text{MONI}}$ ,  $\overline{\text{INTR}}$ , and  $\overline{\text{USER}}$ , all the other keys cause the LED lamp to blink and the speaker to generate a sound.

The PC6 is used for single step execution of a program or when break points exist in a program. Bit  $\emptyset$  through bit 5 are connected to the LED displays and the keyboard matrix. Bit  $\emptyset$  selects the rightmost LED display and bit 5 selects the leftmost LED display. All these bits are active high.

Thus PCØ through PC5 are used for selecting LED display. For example, when PCØ is high, the rightmost display of the LED displays is active.

You may have noticed that the parallel lines of Port B and C first go through three blocks marked with 75492. The three blocks are actually three ICs used as drivers that amplify the incoming signals and convert them into strong signals.

When you use a cassette tape recorder to read data to the MPF-I CPU, the data goes into the CPU through PA7. When the CPU of MPF-I writes data into a cassette tape, the data goes to the cassette tape through PC7.

#### 4 • 15 Advanced Hardware Description (Optional)

### 4.15.1 PIO: Parallel I/O Circuit

The Z80 parallel I/O circuit (PIO) is one of a set of chips manufactured to facilitate Z80 interfacing. The PIO circuit is designed to provide a two-port, programmable, TTL compatible parallel data transfer between the Z80 CPU and peripheral devices. Turn to schematic sheet 3 of 4. In the D and C of column 4, you can find Port A and Port B. The two ports are independent 8-bit parallel bidirectional peripheral interface ports using "handshake" data transfer method.

The Z80 PIO is an IC chip with 40 pins. Of the 40 pins, D0 through D7 is used as Z80 CPU data bus. This is a bidirectional, tristate bus which is used to transfer all data and commands between the CPU and PIO.

# 4 • 15 • 2 CTC: Counter-Timer Circuit

The Z80 counter-timer circuit, like the Z80 PIO circuit is one of a group of IC chips manufactured to facilitate Z80 CPU interfacing. This chip performs timing and event counting functions with four independent 8-bit channels which interface directly to the Z80 data bus.

The CTC chip is used when a program requires that certain operations be performed at fixed time intervals or at pre-set frequencies. In general, the relationship between the CTC and CPU can be regarded as that between a person and his or her watch. The CTC is a 2%-pin chip with eight pins (DØ through D7) used as CPU data bus, seven pins used as CTC control, three pins as interrupt commonly and another seven pins as channel signals. The remaining three pins are pin 24 (to which a 5-volt power is supplied), pin 5 (ground), and pin 15 (which receives a one-phase 5-volt clock pulse).

# 4 · 16 Power Supply

A power adaptor is supplied together with the MPF-I so that you can convert the higher voltage typically supplied by a wall outlet to 9V at 600mA.

The MPF-I requires a single 5V power supply at 500mA. A regulator is installed right beneath the socket for the power adaptor to convert 9-volts to 5-volts. A heat sink may or may not be attached to the voltage regulator to dissipate the heat of the voltage regulator. Don't touch the voltage regulator. It makes your finger uncomfortable.

# **Questions**

4-1. Turn to section 1.3 Physical Configuration of MPF-I User's Manual. Using the information on this page draw a circle around the Z80 CPU.

# Physical Configuration

Fig 4-4

4-2. In Appendix B there are four pages of schematics. Look in the lower right hand corner.

Fig 4-5

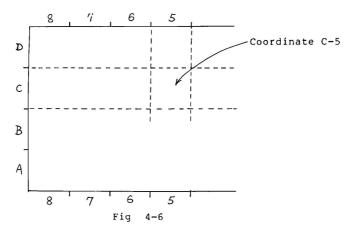

Below the title MPF-I there is an entry indicating which sheet you are reading. In the figure above this is sheet 2 of 4. Find sheet 1 of 4. Notice that to locate any component there are coordinates on the boarders Fig 4-6.

Locate the component at C-5. What is this component? This part also has a U number what is it?  $\_$

4-3. The Z80-CPU transfers data in and out through its' data pins There are eight data pins that are all accessed at one time. The eight pins are grouped under the name data bus. Turn to the diagram CPU PIN-OUTS Appendix C page C-1. Locate the DATA BUS. D0 is the least significant binary digit and D7 is most significant binary digit. Fill in chart below

| BINARY DIGIT | D7 | D6 | D5 | D4 | D3 | D2 | Dl | DØ |

|--------------|----|----|----|----|----|----|----|----|

| PIN NUMBER   |    |    |    |    |    |    |    |    |

When you filled in the chart above, you probably observed that the pin numbers for the data bus are not sequential. The pin numbers jump all around. There is no requirement that pin numbers for a bus be sequential.

- 4-4. Find the RAM in one of the sheets of the schematics in Appendix B (it is labeled U8). What sheet is the RAM on . What are the coordinates of the RAM? . Around the edges of the chip are the pin numbers and their functions. In the center you will see HM6116. A 6116 is a type of RAM. Also on the chip is a memory address. The unit as delivered has the 6116 RAM located at addresses 1800H to 1FFFH.

- 4-5. Again refer to the MPF-I schematics. Find U6 the monitor ROM. What sheet is it on? . What are the coordinates? . Notice the type of allowable chips written on U6-- a 25 $\overline{16}$  or 2532. The 25 $\overline{16}$  option allows 2048 bytes or characters (2K=16K of bits) of information to be retained by the 25 $\overline{16}$ . How many bytes would you think the 2532 chip allows to be retained?

- 4-6. The Z80 CPU is able to address memory chips by connecting the address bus to the Z80 CPU and to the memory chip. The individual lines of the address are labeled A0 to A15. Find the address bus from the Z80 CPU (U1) to the monitor ROM at U6. Enter the pin connections of Z80 CPU and U6 in the chart below.

| ADDRESS BUS<br>PIN NAME  | A15 | A14 | A13 | A12 | All | AlØ | Α9 | A8 | A7 | <b>A</b> 6 | A5 | A4 | АЗ | A2 | Al | ΑØ |

|--------------------------|-----|-----|-----|-----|-----|-----|----|----|----|------------|----|----|----|----|----|----|

| Z8Ø CPU (U1)<br>PIN NAME |     |     |     |     |     |     |    |    |    |            |    | ,  |    |    |    |    |

| RAM (U6)<br>PIN NAME     |     |     |     |     |     |     |    |    |    |            |    |    |    |    |    |    |

Although it may be clear to you from reading the schematic the address (and data) lines travel under U6. This means that A0 of the Z80 CPU is connected to A0 of U7 and A0 of U8. Enter the corresponding pin connections in the chart below.

| ADDRESS BUS<br>PIN NAME  | A15 | A14 | A13 | A12 | All | Alø | Α9 | A8 | Α7 | A6 | Α5 | A4 | A3 | A2 | Al | AØ |

|--------------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Z8Ø CPU (U1)<br>PIN NAME |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

| RAM (U8)<br>PIN NAME     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

4-7. The data bus connects to several ICS just as the address bus does. Find the data bus on sheet 1 of 4. Enter the corresponding connections (pin numbers) in the chart below

| DATA   | BUS | PIN | NAME | D7 | D6 | D5 | D4 | D3 | D2 | Dl | DØ |

|--------|-----|-----|------|----|----|----|----|----|----|----|----|

| Z8ØCPU |     |     |      |    |    |    |    | 14 |    |    |    |

| ROM (U |     |     |      |    |    |    |    | 9  |    |    |    |

The entire data bus is also used to access information from devices such as the keyboard. The 8255(U14) controls the keyboard so the data bus must be connected to this chip. This is so that the 8255 can send keyboard information to the CPU. Look at sheet 2 of 4 coordicates C-8 and D-8. You will see lines (wires) with the labels DØ to D7. Where did these lines come from? To the left of DØ through D7 is a parenthesis labeled SH1,3. SH stands for sheet. The data lines leave sheet 2 of 4 and connect to sheets 1 and 3. Can you find the connection on sheet 1? What are the coordinates? What are coordinates for the data bus on sheet 3 of 4?

# **Answers**

4-1

≥ 80 CPU

- 4-2 At C-5 the Z80-CPU. The U number is 1.

- 4-3 BINARY DIGIT D7 D6 D5 D4 D3 D2 D1 D0

PIN NUMBER 13 10 9 7 8 12 15 14

- 4-4 The RAM is on sheet 1 of 4. The coordinates of the RAM are C-2.

- 4-5 The ROM is on sheet 1 of 4.

The coordinates of the ROM are C-4.

The ROM can store (retain) 4096 bytes.

(4K=32K bits).

4-6

| ADDRESS BUS<br>PIN NAME | A15      | A14 | A13 | A12 | All | A10 | A9 | A8 | A7 | A6 | <b>A</b> 5 | A4 | А3 | A2 | Al | AØ |

|-------------------------|----------|-----|-----|-----|-----|-----|----|----|----|----|------------|----|----|----|----|----|

| 280 CPU (U1)            | 5        | 4   | 3   | 2   | 1   | 40  | 39 | 38 | 37 | 36 | 35         | 34 | 33 | 32 | 31 | 30 |

| RAM (U6)<br>PIN NAME    | NOT USED |     |     |     | 18  | 19  | 22 | 23 | 1  | 2  | 3          | 4  | 5  | 6  | 7  | 8  |

| ADDRESS BUS<br>PIN NAME  | AlØ | Α9 | A8 | Α7 | A6 | A5 | A4 | А3 | A2 | Al | AØ |

|--------------------------|-----|----|----|----|----|----|----|----|----|----|----|

| Z80 CPU (U1)<br>PIN NAME | 40  | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 | 31 | 3Ø |

| RAM (U8)<br>PIN NAME     | 19  | 29 | 23 | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

4-7

| DATA BUS PIN   | NAME   | D7 | D6 | D5 | D4 | D3 | D2 | Dl | DØ |

|----------------|--------|----|----|----|----|----|----|----|----|

| Z8ØCPU (U1) PI | N NAME | 13 | 10 | 9  | 7  | 8  | 12 | 15 | 14 |

| ROM (U6) PIN   | I NAME | 17 | 16 | 15 | 14 | 13 | 11 | 10 | 9  |

| RAM (U8) PIN N | AME    | 17 | 16 | 15 | 14 | 13 | 11 | 10 | 9  |

The coordinates of the data bus on sheet 1 of 4 are D-1. The coordinates of the data bus on sheet 3 of 4 are C-7 and D-7.

# CHAPTER 5

Introduction to Programming the MPF-I

# 5 • 1 Learn by Doing

You will now be guided through a series of examples from the MPF-I User's Manual. You should first key in the example and execute the program. But if you want to learn programming, you must do more. Each example will be analyzed—some examples in great detail. Whenever a new instruction occurs, you will be shown:

- 1) how to test if it is in the Z80 instruction set.

- 2) the correspondence between assembly code and object code.

- what registers, flags and memory locations are affected by the instruction.

- 4) and finally the reason for using the instruction.

# 5 · 2 Flashing a Message

Turn to EXAMPLE 2 in section 5.10. Key in and execute this example. Does the program flash HELP US for 500 ms (1/2 second) and then go blank for 500 ms? Actually you should see HELP US for a longer time than 500 ms and blank screen for less than 500 ms. The program lights the screen for 500 ms but the display takes a period of time to extinguish (fade out) when they are no longer selected.

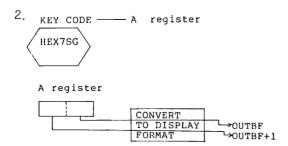

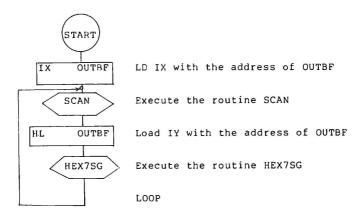

Hex 37 = H

# 5 · 3 Program Analysis

Exercise 5-1

Statement 1: flash 'HELP US'

You must understand you are writing your program in a highly readable form. Some words in your program will not be translated into an object program. An example is the comment statment, like statement 1. When using an assembler to translate your source program into object code, the comment statement must start with a semicolon. The semicolon signals the assembler to ignore the comment statement. Why use a comment statement? Comments are used to make the program understandable to readers and to programmers. Such statements are called documentation. A comment statement helps document a program.

52

Ex 5-2

$$3F = A$$

$A7 = D$

$BE = 9$

$3S = C$

$BA = S$

$SF = F$

$SF = F$

$SF = F$

$SF = H$

$SS = C$

$S$

#### Statement 2: ORG 1800H

The ORG statement informs the assembler where to place the translated code. ORG stands for origin — a beginning. When the assembler sees an ORG statement, it sets a counter which determines the location of each translated instruction. This location counter is advanced as each instruction is converted into object code.

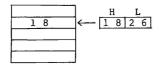

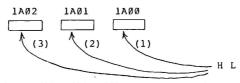

# Statement 3: LD HL, BLANK

This statement loads the address of BLANK into the register pair HL. To determine the address of BLANK, refer to line 19. BLANK is a label and thus is in the column (field) where labels are located. The address of LABEL, 1826, is given by the lefthand column. The location counter is responsible for calculating the values in this column. It has now been determined that statement 3 loads the value 1826 into the HL register pair. The H can be assumed to standfor high, thus the high byte, 18, is loaded into the H register. L means low, so the low byte, 26, is loaded into the L register.

When you are writing a program, you need to know what the instruction set is. Can the register pair HL be loaded with a value given in the instruction (BLANK)? This value is called an immediate, because you can look at the object code and immediately see the numbers being loaded into the registers.

To determine the legality of LD HL, BLANK, you need to know two facts: 1) is there an H and an L register which can they be paired and 2) is the instruction allowable. determine the first fact, turn to Appendix C and find the page titled Z-80 CPU REGISTER CONFIGURATION. Yes, near the top of the page under MAIN REGISTER SET you see H and L. The Z80 REGISTER CONFIGURATION is also shown in fig 5-1 (and fig 5-2). Now look in Appendix C for the page with the title 16-BIT LOAD GROUP 'LD' 'PUSH' and 'POP'. The SOURCE at the top of the chart then REGISTER Under REGISTER the fourth entry over from the below SOURCE. left contains HL, thus H and L may be paired. But are H and L being used as a source in the instruction LD HL, BLANK? No, the BLANK is being loaded into HL, therefore, HL is a destination. Looking on the left side of the chart, find DESTINATION then REGISTER. The fourth entry from the top (under REGISTER) is HL. So HL can be used as a destination. Can an immediate value be loaded into HL? Travel from left to right in the row labeled HL until you come to the column labled IMM.EXT (immediate extended). At the intersection of the row and column, there is value (21). A box with a value in it means that the instruction is allowed. Each "n" in the box stands for one byte. The upper "n" is the value to be loaded into L, and the lower byte is the value to be loaded into H.

Fig 5-l

| d Group                 |                     |         |    |                      |               |              |               |               |               | Ì             | - /           |                |   |

|-------------------------|---------------------|---------|----|----------------------|---------------|--------------|---------------|---------------|---------------|---------------|---------------|----------------|---|

|                         |                     |         |    |                      |               |              | so            | URCE          |               | /             | 0.520         |                |   |

|                         |                     |         |    |                      | P             | EGIST        | ER            |               |               | IMM,<br>EXT.  | EXT.<br>ADDR. | REG.<br>INDIR. |   |

|                         |                     |         | AF | вс                   | DE            | HL           | SP            | IX            | IY            | nn            | (nn)          | (SP)           | İ |

|                         |                     | AF      |    |                      |               |              | :             |               |               |               |               | F1             |   |

| DESTINATION (1) (2) (3) |                     | вс      |    |                      |               |              |               |               |               | 01<br>n       | ED<br>4B<br>n | C1             |   |

|                         |                     | DE      |    |                      |               |              |               | (5)           | \             | 11<br>n       | ED<br>58<br>n | D1             |   |

|                         | REGISTER            | HL<br>J |    |                      |               |              |               |               |               | 21<br>1 n     | n 2A E1 n ED  | E1             |   |

|                         |                     | SP      |    |                      |               | F9           |               | DD<br>F9      | FD<br>F9      | 31<br>n<br>n  | ED<br>78<br>n | 2A E1          |   |

|                         |                     | ΙX      |    |                      |               |              |               |               |               | DD<br>21<br>n | DD<br>2A<br>n |                |   |

|                         |                     | IY      |    |                      |               |              |               |               |               | FD<br>21<br>n | FD<br>2A<br>n | FD<br>E1       |   |

|                         | EXTERNAL<br>ADDRESS | (nn)    |    | ED .<br>43<br>n<br>n | ED<br>53<br>n | 22<br>n<br>n | ED<br>73<br>n | DD<br>22<br>n | FD<br>22<br>n |               |               |                |   |

| PUSH<br>INSTRUCTIONS    | REGISTER<br>IND.    | (SP)    | F5 | C5                   | D5            | E5           |               | DD<br>E5      | FD<br>E5      |               |               |                |   |

(4)

NOTE: The Push & Pop Instructions adjust the SP after every execution.

Fig 5-2

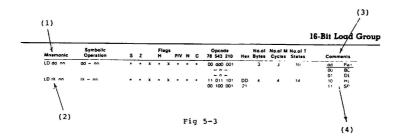

The correct form for the source code can be found on the next page titled 16-BIT LOAD GROUP (see fig 5-3 also). On the leftmost column is the mnemonic column. Mnemonic means assisting or intended to assist the memory. below the title MNENOMIC is the form for load immediate, LD dd, nn. The LD, of course, means load. "nn" is the immediate value - BLANK (1826) in statement 3. To understand "dd" locate the column labeled COMMENTS on the far right. "dd" tells the programmer what register pairs can be used in the 16 bit load immediate instruction. Thus;

LD BC,nn LD DE,nn LD HL,nn LD SP,nn

are allowed. To complete the LD HL,nn instruction, simply fill the value for nn , e.g., LD HL,BLANK. LD HL,1826H would produce the same result.

If you are hand translating the assembly language instructions you must use the chart on the previous page. Remember that 21nn that was found at the intersection of HL and IMM.EXT 21 is called the opcode (operation code). The translation gives

2 1 2 6 1 8

Why wasn't the result of the translation

2 1 1 8 2 6

Because the low byte 26 must follow the opcode, then the high byte 18. Don't fight it! You must write values this way in Z80 coding. LD HL,BLANK translates into a 3 byte instruction. The location counter will be advanced by 3 in preparation for the next instruction  $1800 + 3 \longrightarrow 1803$ . In summary:

Location Counter Object Code Statement No. Source Code

1800 212618 · 3 LD HL, BLANK

Ex 5-3

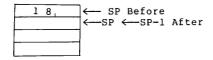

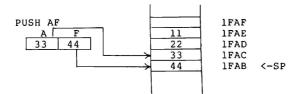

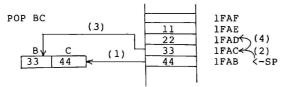

Statement 4: PUSH HL

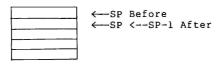

The PUSH instruction is used to move the contents of a register pair or a 16-bit register to a specific place in memory. To determine the assembly language code mnemonic, turn to Appendix C and proceed to the chart 16-BIT LOAD GROUP. Travel down the leftmost column labled Mnemonic until the mnemonic PUSH is located. Since "qq" means that BC, DE, HL and AF are allowed, this is the correct form. To translate the instruction into machine language, refer to the chart 16-BIT LOAD GROUP 'LD' 'PUSH' and 'POP'. The source is the content of the HL register pair. Find SOURCE, Register and then HL. For destination find the title PUSH INSTRUCTIONS at lower left hand part of the page. Where the column HL and row PUSH INSTRUCTIONS meet is the value E5. This is the value you will enter. This one byte instruction advances the location counter by one 1803+1 -->

Details of the push instruction.

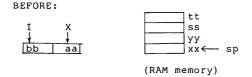

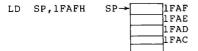

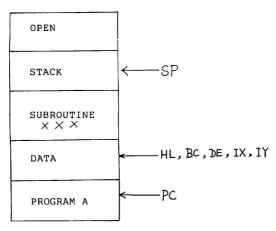

A PUSH instruction transfers the contents of registers to a region in memory called the stack. The stack is defined by a pointer called a Stack Pointer (sp). In EXAMPLE 2 the stack pointer was set by the monitor before you began execution of the program.

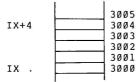

STEPS IN THE EXECUTION OF PUSH HL

STEP 1: DECREMENT THE STACK POINTER

RAM memory

STEP 2: PUSH H ONTO THE STACK

STEP 3: DECREMENT THE STACK POINTER

STEP 4: PUSH L ONTO THE STACK

58

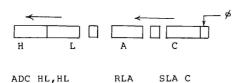

#### Statement 5: LD IX, HELP

This statement is very similar to statement 3. It is a load immediate instruction. The 16 bit register IX is being loaded instead of the register pair HL. The immediate value is 1820H (see statement 13). There is something new besides using index register IX as the destination. instruction has two opcodes. Find the object code for instruction by turning to the 16-BIT LOAD GROUP 'LD' 'PUSH' and 'POP' in Appendix C. The intersection of the source IMM.EXT and destination IX shows DD2lnn. The two opcodes are DD and 21. The reason for the double or extended is because the Z80 CPU, designed by Zilog, is an opcode improved 8080 (an earlier CPU designed by INTEL). Zilog wanted the Z80 CPU to be able to execute all of the 8080instructions plus the ability to execute new instructions. Some opcodes were not used by the 8080 CPU. If only one opcode was used in the empty slots (unused 8080 opcodes), only a few new instructions could be added. A double opcode allows the DD to be followed by one of 256 different codes (00H to FFH). Now in place of one unused opcode, many new instructions can be added. If you look at the row labeled IX, you will see that all the instructions have as the first opcode a DD. HELP is a label in statement 13. The value of the location counter at this point is 1820. When you translate LD IX, HELP to object code, the nn (2 bytes) will contain 1820. The object code for LD IX, HELP is DD 21 20 18. Don't forget the lower order byte 20 is written first followed by the high part of the address 18. LD IX, HELP is a four byte instruction. The location counter will advance by  $4\ 1804 + 4 = 1808$

Ex 5-5

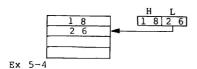

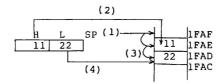

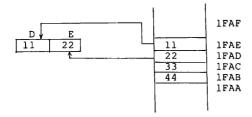

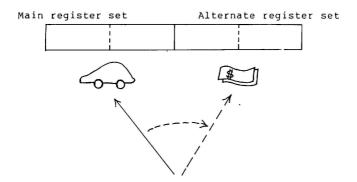

Statement 6: LOOP EX (SP), IX

The instruction asks the computer to EXchange the two byte pair currently pointed to by the stack pointer with the contents of the IX register.

AFTER:

(RAM memory)

The first time this instruction is executed, the stack will contain 1820H and IX will contain 1826H. Because of the exchange, the next time this instruction is used the stack will contain 1826H and IX will contain 1820H. The action of EX (SP),IX is to make index register IX alternate between pointing to the message HELP US at 1820H and the blank display at 1826H. Enclosing an instruction in parentheses indicates a memory reference. The stack pointer is enclosed by parentheses (SP) thus the stack points to memory.

Ex 5-6

Statement 7: LD B,50

The constant (immediate value) is loaded into the  ${\rm \acute{E}}$  register. The exercise Ex 5-7 will explain this instruction.

EX 5-7

Statement 8: CALL SCAN1

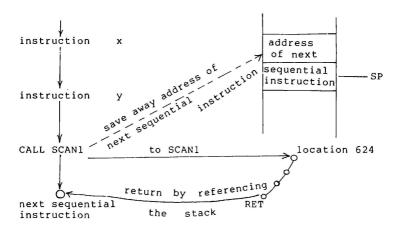

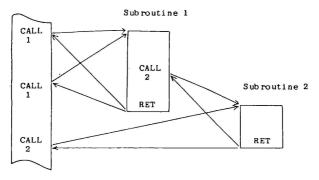

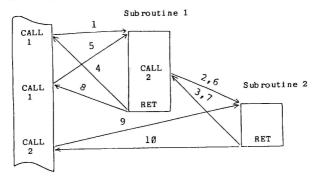

A series of instructions which perform a definite task is called a routine. A program consists of one or more routines. The monitor contains several routines which the user may wish to access. SCANI is a monitor routine which will (as one of its actions) display the area pointed to by IX. The display consists of 6 sections so IX will point to a six byte region. A routine accessed by another routine or program can be called a subroutine. The CALL instruction is the preferred method to access a subroutine.

The CALL instruction breaks the sequential processing of instructions by transferring control to a new address. In statement 8 the new address is the entry point into the routine SCAN1. The execution of SCAN1 is terminated by a return (RET) instruction. The return instruction is used to order program control to continue just after the CALL instruction.

How a CALL-RET Works CALL SCAN1

In reality when CALL SCAN1 is executed, the contents of the program counter (PC) which already points to the next sequential instruction are saved on the stack. The contents of the PC (180F), in Example 2, are pushed (saved) on the stack. Now the program counter is loaded with the subroutine address given the CALL SCAN1 instruction. (in this example the address is 0624H, SCAN1). Program control is now transferred to SCAN1. When the return (RET) instruction in SCAN1 is executed, the program counter will be loaded from the stack. The value on the stack is the address of the next instruction after SCAN1, so control returns to location 180FH.

After the above explanation you may have forgotten what's happening. The call to SCAN1 will use the six bytes at BLANK to control the screen (displays). Zeros are sent to the display in the MPF-I, which turns off all the segments in a display. So BLANK blanks the screen, but only for a short time.

EX 5-8

Statement 9: DJNZ HELFSEG

Statement 9 provides the solution to the very short time that SCAN1 will blank out the screen. What is needed is a method of repeating statement 8 which will again display the current pattern that the IX register is pointing to.

The DJNZ instruction will:

- 1) Decrement the B register. B was loaded with a 50 (decimal) so it will now contain 49 (decimal).

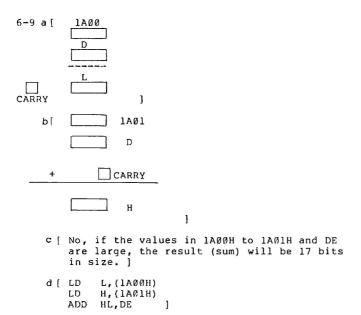

- 2) Compare B with zero.

- 3) If B is not equal to zero, program control is transferred to the location given in the operand field. The operand field contains HELFSEG so, the program continues at the statement containing HELFSEG as a label.