## MULTITECH INDUSTRIAL CORP.

# MPF-I EXPERIMENT MANUAL (SOFTWARE/HARDWARE)

#### COPYRIGHT

Copyright © **1981** by MULTITECH INDUSTRIAL CORP. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of MULTITECH INDUS-TRIAL CORP.

#### DISCLAIMER

MULTITECH INDUSTRIAL CORP. makes no representations or warranties, either express or implied, with respect to the contents hereof and specifically disclaims any warranties or merchantability or fitness for any particular purpose. MULTITECH INDUSTRIAL CORP. software described in this manual is sold or licensed "as is". Should the programs prove defective following their purchase, the buyer (and not MULTITECH INDUSTRIAL CORP., its distributor, or its dealer) assumes the entire cost of all necessary servicing, repair, and any incidental or consequential damages resulting from any defect in the software. Further, MULTITECH INDUSTRIAL CORP. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of MULTI-TECH INDUSTRIAL CORP. to notify any person of such revision or changes.

## Multitech INDUSTRIAL CORP.

OFFICE/ 9FL, 266 SUNG CHIANG ROAD, TAIPEI 104 TAIWAN R.O.C. TEL:(02)551-1101 TELEX:"19162 MULTIIC" FAX:(02) 542-2805 FACTORY/ 1 INDUSTRIAL E. RD., III HSINCHU SCIENCE - BASED INDUSTRIAL PARK, HSINCHU, TAIWAN, R.O.C.

## PREFACE

The first 50 years of the 20th century witnessed the invention of the internal combustion engine, which greatly extended the physical strength of the human body.

In the second half of the century, the birth of the microprocessor further extended our mental capabilities. Applications of this amazing product in various industries have introduced so much impact on our lives, hence, it is called the second Industrial Revolution.

Microcomputers represent a total change in designing systems. Both industrial and academic institutions are active in the development and search for new applications for microcomputers.

This book is designed to be used in conjunction with the "multitech" MPF-1 Microcomputer as part of a one-year laboratory class on microcomputers. With the aid of this book, students will be able to learn the fundamentals of microcomputers, from basic CPU instructions to practical applications.

The first part of this book is an introduction to the basic concepts of microcomputer programming. It lays the foundation for later studies, the second part of this book is the source list of monitor program, the third part begins with a series of experiments using microcomputer instructions, such as, data transfers, arithmetic and logic operations, jump and subroutine and memory address allocation in simple programs. Experiments involving more complicated arithmetic operations, such as, binary to decimal conversion, decimal to binary conversion, multiplication, division and square root are presented.

There are two experiments in this book which are designed to familiarize the student with the fundamentals of input/output programming. These programs are centered around the keyboard and display. These experiments establish the foundation for later experiments involving a simple monitor program, which leads to more complicated MPF-1 programs.

## MPF-I EXPERIMENT MANUAL

#### TABLE OF CONTENTS

| Preparations | •••• |                                                                      |

|--------------|------|----------------------------------------------------------------------|

| Introduction | Τo [ | Designing Microcomputer Programs                                     |

| Experiment   | -1   | Data-Transfer Experiment                                             |

| Experiment   | -2   | Basic Applications of Arithmetic and<br>Logic Operation Instructions |

| Experiment   | -3   | Binary Addition and Subtraction                                      |

| Experiment   | -4   | Branch Instructions and Program Loops                                |

| Experiment   | -5   | Stack and Subroutines                                                |

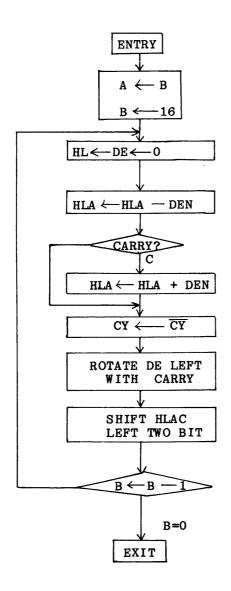

| Experiment   | -6   | Rotate Shift Instructions and multiplication Routines                |

| Experiment   | -7   | Binary Division Routine                                              |

| Experiment   | -8   | Binary-to-BCD Conversion Program55                                   |

| Experiment   | -9   | BCD-to-Binary Conversion Program59                                   |

| Experiment   | -10  | Square-Root Program                                                  |

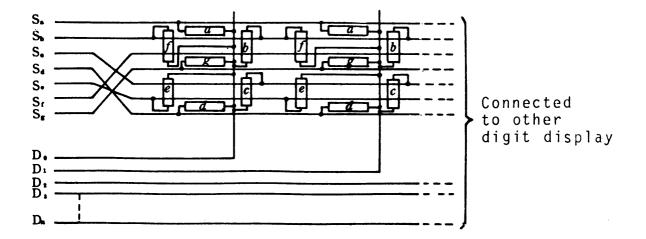

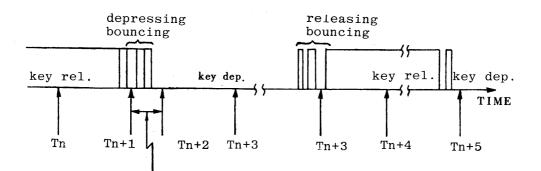

| Experiment   |      | Introduction to MPF-I Display72                                      |

| Experiment   | -12  | Fire-Loop Game                                                       |

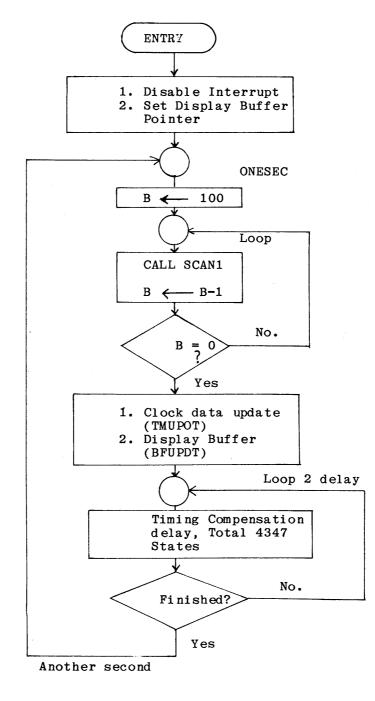

| Experiment   | -13  | Stop-Watch                                                           |

|              |      | Clock 1 (How to design a clock)                                      |

| Experiment   | -15  | Clock 2 (with CTC interrupt mode 2) 103                              |

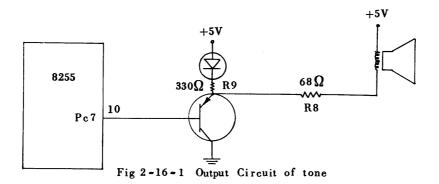

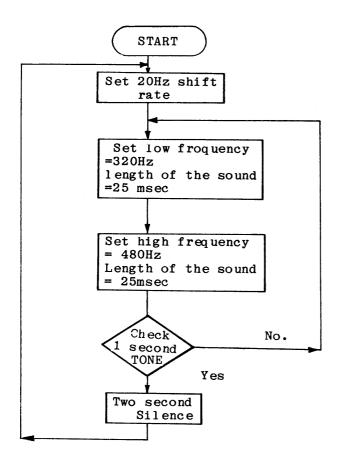

| Experiment   | -16  | Telephone Tone                                                       |

| Experiment   |      |                                                                      |

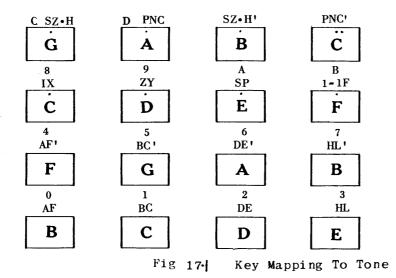

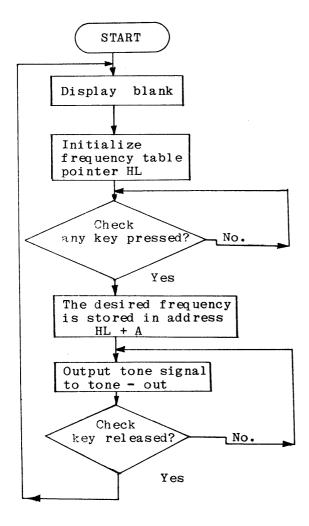

| Experiment   | -18  | Music Box                                                            |

## **Preparations**

## **Introduction To Designing Microcomputer Programs**

A computer program is an organized series of instructions. The central processing unit will perform a series of logical actions to obtain the desired result.

Before a proram is executed by CPU it must be stored in memory in binary form. This type of program is called a "machine language This is the only type of language the computer understands. program". The machine language program is usually represented by Hexadecimal digits. For example, the 8-bit instruction 1010 1111B(B represents binary) in the Z80 CPU it can be replaced by OAFH (H indicates Hexidecimal). Interpreting a machine language program is extremely difficult and time consuming for the User. The microprocessor manufacturer divides the CPU instructions into several categories according to their functions. The CPU instructions and registers are usually represented by symbols called "mnemonics". For example, the Z80 CPU instruction 70H can be represented by the mnemonic code LD A,L (Load Data into register A from register L). A program written in mnemonic codes is called an "assembly language program." Before an assembly language program can be executed by the CPU, it must be translated into machine language by a special software program called an "Assembler".

Normally a program is written in assembly language. The main advantage of assembly language program over machine language programming is that assembly language programming is much faster to code, the mnemonics makes it much easier for the User to remember the instruction set, and normally the assembler will contain a self-diagnostic package for debugging programs. The main disadvantage of assembly language programs is that it requires an assembler and microcomputer development system. These two items are very costly. With the MPF-I microcomputer the User has to translate assembly programs into machine level programs by hand before executing programs

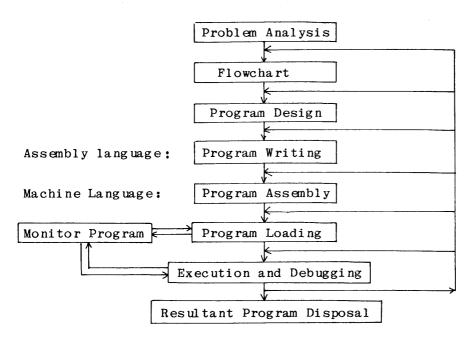

#### A. Problem Analysis

The software program of a simple problem may be easily designed with a well-defined flowchart. It may also be obtained by revising some existing programs or combining some simple routines. The design of more complicated programs, such as monitor programs, system control programs or a special purpose program, are usually started after some detailed analysis of the problem has been made. Problem analysis and solution requires a good understanding of the following:

See page (III-3)

- (1) Characteristic and requirements of the problem

- (2) Conditions which are known

- (3) Input information format and how it is converted

- (4) Output data format and how it is converted

- (5) Type of data and how precise it is

- (6) Execution speed required

- (7) CPU instructions and performance

- (8) Memory size

- (9) The possibility that the problem can be solved

- (10) Methods to solve the problem

- (11) Evaluation of the program

- (12) How the resultant program will be disposed

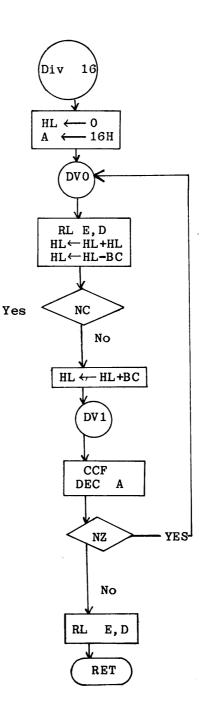

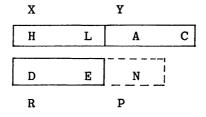

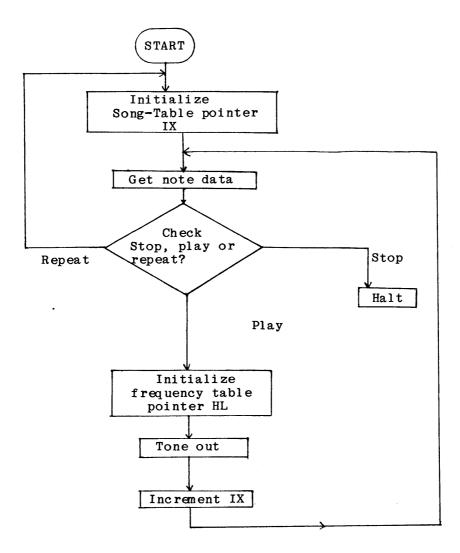

Figure 2-A-1

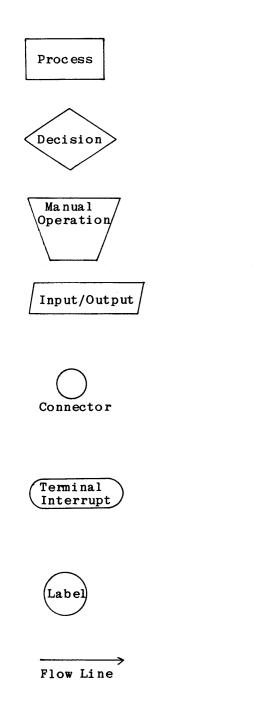

#### **B.** Flowchart

A flowchart can be used to indicate the behavior of algorithms by suitable graphs. Once the complete flowchart has been completed, a full picture of the programmer's thought processes in reaching a solution to the problem may be followed. Flowcharts are especially important in program-debugging. It is an important part of the finished program. It may help other people to understand the exact algorithm used by the programmer.

Two levels of flowcharts are often desirable:

System flowchart -- showing the general flow of the program

Detailed flowchart -- providing details that are of interest mainly to the programmer.

Usually, a complicated program is introduced using a system flowchart outlining the program, and then a detailed flowchart is presented. The advantage of a flowchart is that it emphasizes the sequential nature of steps by using arrows pointing from each step to its successor. Various symbols are used to indicate the operation that is to be performed at each step. Figure 3-A-2 gives some standard symbols used in flowcharts:

\_5

#### C Program Design

There are many types of programs. Programs for mathematical equations, conversion of input and output signals, coding and decoding of the program data, peripheral device drives, etc. are example of simple programs. Assembler, monitor and system control programs or special purpose applications are examples of more complicated programs. The following items are usually considered in program design:

- (1) Acquisition of input signals or data

- (2) Generation or conversion of output signals and data

- (3) Logical analysis and calculations in the main program

- (4) Relation between the main program and subroutines

- (5) Use of internal registers

- (6) Memory allocation of the main program

- (7) Memory allocation of subroutines

- (8) Memory allocation of data tables and indexed addressing method

- (9) System initialization and constants in the program

- (10) Definition of the variables in the program

- (11) Consideration of timing sequences and program execution speed

- (12) Limitations of memory size

- (13) Length and precision of data

- (14) Availability of documents and references

- (15) Other special items

#### **D. Program Writing**

In this book, the programs are written mainly in assembly language. Here only the format of the assembly language program is given.

A statement in the program is composed of four parts : Label, Opcode, Operand and Comment. An example is shown below

| LABEL       | OPCODE                                                  | & OPERAND                                                                 | COMMENT                                                   |

|-------------|---------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------|

| DTB4<br>DB3 | SRL<br>RR<br>RR<br>LD<br>CALL<br>LD<br>LD<br>CALL<br>LD | B,16<br>H<br>L<br>D<br>E<br>A,H<br>DB1<br>H,A<br>A,L<br>DB4<br>L,A<br>DB3 | ; ROTATE HL DE RIGHT<br>; CORRECT H<br>; BINARY CORRECT L |

| BINAR       | Y CORREC                                                | CT ROUTINE                                                                |                                                           |

| D <b>B4</b> | BIT<br>JR<br>SUB                                        | Z, DB1                                                                    | ; IF BIT 7 OF A = 1, SUB FROM 30H                         |

| DB1         |                                                         | 3, A<br>Z, DB2<br>3                                                       | ; IF BIT 3 OF A = 1, SUB FROM 03H                         |

| DB2         | RET                                                     |                                                                           |                                                           |

Sometimes, a program statement without a comment is not easy to understand. The comments in the statements are very important especially for a complicated program. Statements with a label and comment field are more convenient for calling and debugging.

#### E. Program Assembly

Using the resident assembler in a microcomputer system is an effective way to assemble the source program. However, a beginner or a proram designer not familiar with the microcomputer development system must assemble his/her program by hand. The usual procedure for hand assembly is:

- (1) Translate each instruction (mnemonic) into the machine code by looking it up in the conversion table. The comment field of each statement is ignored.

- (2) After deciding the starting address of the program. Assign an appropriate address to the first byte of each instruction. The exact number of bytes needed must be reserved including space for instructions such as JR, DJNZ, and destination addresses of instructions JP, CALL, etc.

- (3) Calculate the relative displacement and put it in the assembled program. A simple formula for calculating the relative displacement is:

displacement = (destination address) - (next instruction address)

If the calculated result is positive, then it is the desired value. If the calculated result is negative, then subtract the result from 100II (i.e. take its 2's complement) and the final result is taken as the operand of this instruction. For instance, in the program listed above, the instruction DJNZ DB3 at address 0014H is first translated into 10xx and then the xx value is calculated.

xx = 0002H (destination address) - 1016H (next instruction's address) = -14H (negative value) xx = 100H - 14H = 0ECH

Therefore, the instruction DJNZ DB3 must be translated into 10EC. In addition, the instruction JR Z, DB 1 at address 0019H is first translated into 28xx, and then the xx value is calculated.

xx = 001DH (destination address) - 001BH (next instruction's address) = 2 H

The instruction JR Z, DB 1 must be translated into 2802.

The translated machine language is given below:

| Machine<br>Address Language I | Label Opcode & Operand Comment                                           |  |

|-------------------------------|--------------------------------------------------------------------------|--|

|                               |                                                                          |  |

|                               | ** 4 DIGIT BCD TO BINARY CONVERTION ROUTINE **<br>EXTRY : BCD DATA IN HL |  |

|                               | EXIT : BINARY DATA IN DE<br>REGISTER CHANGED : AF BC DE HL               |  |

| 0000<br>0002<br>0004<br>0006 | 0610<br>CB3C<br>CB1D<br>CB1A | DTB4<br>DB3 | LD<br>SRL<br>RR<br>RR | B,16<br>H<br>L<br>D | ;  | B | 3 = | • BI' | г   | COUI | T   |    |          |     |      |     |

|------------------------------|------------------------------|-------------|-----------------------|---------------------|----|---|-----|-------|-----|------|-----|----|----------|-----|------|-----|

| 0008                         | CB1B                         |             | RR                    | E                   | ;  | R | loi | ATE   | HI  | D    | E F | 10 | HT       |     |      |     |

| A000                         | 7C                           |             | LD                    | A,H                 |    |   |     |       |     |      |     |    |          |     |      |     |

| 000B                         | CD1D00                       |             | CALL                  | DB1                 |    |   |     |       |     | •    |     |    |          |     |      |     |

| 000E                         | 67                           |             | LD                    | H,A                 | ;  | C | COR | REC   | r i | 1    |     |    |          |     |      |     |

| 000F                         | 7D                           |             | LD                    | A,L                 |    |   |     |       |     |      |     |    |          |     |      |     |

| 0010                         | CD1700                       |             | CALL                  | DB4                 |    |   | _   |       | _   |      |     |    |          |     |      |     |

| 0013                         | 6F                           |             | LD                    | L,A                 | ;  | E | BIN | ARY   | C   | DRR  | ECI | ΓI | <u> </u> |     |      |     |

| 0014                         | 10EC                         |             | DJNZ                  | DB 3                |    |   |     |       |     |      |     |    |          |     |      |     |

| 0016                         | C9                           |             | RET                   |                     |    |   |     |       |     |      |     |    |          |     |      |     |

|                              |                              | ;           |                       |                     |    |   |     |       |     |      |     |    |          |     |      |     |

|                              |                              | ; BINAR     | Y CORREC              | T ROUNTI            | NE | } |     |       |     |      |     |    |          |     |      |     |

| 0017                         | CB7F                         | DB4         | BIT                   | 7,A                 |    |   |     |       |     |      |     |    |          |     |      |     |

| 0019                         | 2802                         |             | JR                    | Z,DB1               | ;  | ] | [F  | BIT   | 7   | OF   | A   | =  | 1,       | SUB | FROM | 30H |

| 001B                         | D630                         |             | SUB                   | 30H                 |    |   |     |       |     |      |     |    |          |     |      |     |

| 001D                         | CB5F                         | DB1         | BIT                   | 3,A                 |    |   |     |       |     |      |     |    |          |     |      |     |

| 001F                         | 2802                         |             | JR                    | Z, DB2              | ;  | ] | [F  | BIT   | 3   | OF   | A   | =  | 1,       | SUB | FROM | 03H |

| 0021                         | D603                         |             | SUB                   | 3                   |    |   |     |       |     |      |     |    |          |     |      |     |

| 0023                         | С9                           | DB2         | RET                   |                     |    |   |     |       |     |      |     |    |          |     |      |     |

#### F. Program Loading

The monitor program can be used to assist the user in loading the program into the reserved memory address in MPF-I. The program can be inputted from the keyboard or read from a magnetic tape. After the prgram is loaded into MPF-I RAM, an error-checking process is required to eliminate any errors. Redundant instructions or data may be replaced by an "NOP" instruction. Missed instructions or data are inserted into the desired addresses by using the Block Data Transfer method or simply by reloading the program. While revising the program, it is very important to check whether Jump instructions (JP, JR, DJNZ, CALL, etc.) are affected by the the change in memory addresses. If this happens, then make the necessary correction(s) immediately.

#### G. Program Execution and Debugging

Before executing a program, it is necessary to set the initialization parameters and set the program counter at the starting address of the program. Pressing the GO key will start the program execution. After the program execution is completed, check the result. If there is any error, the program must be checked step by step with the aid of the monitor program. After the program is revised, execute it again and check the result agian.

## **Experiment** 1

### **Data-Transfer Experiment**

Purposes:

- 1. To familiarize the user with the function of data-transfer instruction

- 2. To practise setting the initial value of data

- 3. To practise assembling, loading and executing a program

Time required: 4 hours

I. Theorectical Background:

- Most of the data-transfer operation is accomplished by using LD (load) instructions. Data can be transferred in units of 8 bits or 16 bits. Also, instructions such as EX, EXX, PUSH and POP can be used to transfer 16-bit data. Instructions such as LDI and LDIR can be used to transfer blocks of data by moving a series of bytes.

- 2. A LD instruction must include two operands. The first operand represents the location where data will be stored (register or memory section). This is called its "destination". The second operand represents the original location of the data to be transferred. This is called the "source". For instance, LD A,B indicates that data in register B will be transferred to register A. Register A is the "destination" and Register B is the "source".

| 3. | The | direction | of | data | transfer | may | be: |

|----|-----|-----------|----|------|----------|-----|-----|

|    |     |           |    |      |          |     |     |

| <u> </u> | diffection of data transfer | may ~ | ••  |          |   |             |

|----------|-----------------------------|-------|-----|----------|---|-------------|

|          | (1) register <- register    | e.g.  | LD  |          |   | LD HL,BC    |

|          | (2) register <- memory      | e.g.  | LD  | A,(HL)   | ; | POP AF      |

|          | (3) register <- immediate   | data  |     |          |   |             |

|          |                             |       |     |          |   | LD HL,125AH |

|          | (4) memory <- register      | e.g.  | LD  | (HL),A   | ; | PUSH BC     |

|          | (5) memory <- memory        | e.g.  | LDD |          | ; | LDIR        |

|          | (6) memory <- immediate da  | ata   |     |          |   |             |

|          |                             | e.g.  | LD  | (HL),5BH | [ |             |

|          |                             |       |     |          |   |             |

II. Experiment 1-1

Write an assembly language program to set the contents of the registers as follows : A=0, B=1, C=2, D=3, E=4, H=5, L=6 (use 8-bit LD instructions to transfer one byte of data each time).

Step 1 Write the assembly language program in the following blank form. The last instruction is RST 38H which returns control of the MPF-I to the monitor program after executing the whole program.

- Step 2 Using the table of 8-bit LD instructions, translate the program into machine language with the starting address at 1800H. Assign the proper address to each instruction.

- Step 3 Prepare the MPF-I microcomputer. Key in the program from the keyboard. Check the program stored in memory. Set the PC (program counter) to the starting address 1800H and execute the program.

- Step 4 Press the REG key and check if the content of each register is correct. If there is any error then return to step 1 and recheck.

| Memory<br>Address | Machine<br>Language | Assenbly<br>Language |

|-------------------|---------------------|----------------------|

| 1800H             | 3E00                | LD A,O               |

| •                 | •                   |                      |

| •                 | •                   | . <b>.</b>           |

| •                 | •                   | ·•                   |

|                   | FF                  | RST 38H              |

III. Experiment 1-2

Write an assembly language program to set the contents of registers as follows: B=12, C=34, D=56, E=78, H=9, L=A (use 16-bit LD instruction to transfer two bytes of data each time).

Step 1 Same as in Experiment 2-1-1 (Write an assembly language program).

- Step 2 Using the 16-bit LD instruction table, translate the program into machine language with starting address at 1820H. Assign the proper address to each instruction.

- Step 3 Load the program (same as Experiment 2-1-1). Set the PC to 1820H and execute the program.

- Step 4 Check contents of each register same as Experiment 2-1-1.

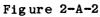

- Note A 16-bit piece of data is composed of two bytes of data. The high-order byte is in the higher memory address and the low-order byte is in the lower meory address. For instance, the 16-bit data 1234H is stored in addresses 1820H - 1821H in the following way:

memory contents

memory address

| Address      | Machine<br>Language | Assembly<br>Language |

|--------------|---------------------|----------------------|

| Auu 1 655    |                     |                      |

|              |                     |                      |

| <u>1820H</u> | 013412              | LD BC,1234H          |

| <u>1823H</u> |                     |                      |

|              |                     |                      |

|              | ' <u> </u>          | RST 38H              |

Example :

Write a program to clear the contents of memory addresses 1850H - 186FH.

Explanation:

16-bit data

- (1) If we use an 8-bit LD instruction to transfer the data to each destination, then 32 (20H) executions of data-transfer is required. It is more convenient to use the loop method in the program.

- (2) Use register B as a loop counter. Set register B equal to 20H before the loop program is executed. Use HL as the memory address pointer and set HL to the starting address 1850H. HL is incremented by one and B is decremented by one for each loop. If B=0, then all loops have been executed; otherwise, run the loop again.

- (3) The program is given below:

| Address  | Machine<br>Language | Label | Opcode | & Operand | Comment                                |

|----------|---------------------|-------|--------|-----------|----------------------------------------|

| 1800     |                     |       | LD     | В,20Н     | ; Set loop counter equal to 32         |

|          |                     | - ,   | LD     | HL,1850H  | ; Set HL equal to the starting address |

|          |                     |       |        |           | ; of memory to be cleared              |

| <b>.</b> |                     |       | XOR    | A         | ; Set A=0                              |

|          |                     | LOOP  | LD     | (HL),A    | ; Load 0 into the memory address       |

|          |                     |       |        |           | ; pointed to by HL                     |

|          |                     |       | INC    | HL        | ; Increment HL by 1                    |

|          |                     |       | DEC    | В         | ; Decrement B by 1                     |

|          |                     |       | JR     | NZ,LOOP   | ; If B not = 0, return to LOOP         |

|          | FF                  |       | RST    | 38H       | ; Return to the monitor program        |

|          |                     |       |        |           |                                        |

IV. Experiment 1-3

Translate the program in Example 1-1 into machine language and load it into MPF-I RAM. Then, execute the program and check if the contents of 1850H - 186FH have been cleared. If not, correct the program and execute it again.

$V_{.}$  Experiment 1-4

Write an assembly language program to set the contents of memory address 1840H - 184FH as follows: 0, 1, 2, 3, ....F.

(HINT: Change the loop counter and the value of the starting address. register A is incremented by '1' in the next loop)  $\label{eq:higher}$

| ADDRESS | MACH INE<br>LANGUAGE | LABEL | OPCODE & OPERAND |

|---------|----------------------|-------|------------------|

|         |                      | ***** |                  |

|         |                      |       |                  |

|         |                      |       |                  |

|         |                      |       | *****            |

|         |                      |       |                  |

## Experiment 2 Basic Applications of Arithmetic and Logic Operation Instructions

Purposes:

- 1. To familiarize the user with the arithmetic and logic operation instructions

- 2. To understand the memory addressing mode

- 3. To understand the meaning of the register status flag

- 4. To practise arranging data for CPU registers and memory sections

Time Required: 4 hours

I. Theoretical Background:

1. 8-bit arithmetic and logic operation instructions:

The 8-bit arithmetic and logic operations in the Z80 CPU are performed in register A (accumulator). Registers A, B, C, D, E, H, and L can be used as operands in conjunction with register A in the LD instructions. If data are transferred between memory and register A, the memory address can be pointed to by HL, IX or IY registers. The meaning of the following instructions are given in the right-side comment field:

(1) ADD A ; Data in register A is added to itself, i.e. the data is doubled shifted left one bit. (2) ADC B ; Register B and the carry flag are added to register A. (3) SUB C ; Data in register C is subtracted from register A. (4) SBC (HL) ; Subtract the data in the memory address pointed to by HL and the contents of the carry flag from register A. ; Logical "AND" of register D and register A. (5) AND D (6) OR OFH ; Logical "OR" of data OFH and register A . (7) XOR A ; Exclusive "OR" register A and itself. (Since register A is equal to register A, the result is zero). (8) INC H ; Increment the contents of register H by 1. (9) INC (IX) ; Increment the contents of the memory address pointed to by register IX by 1. (10) DEC C ; Decrement the contents of register C by 1.

\_15

#### 2. Data Addressing Mode

In the above assembly language instructions, the addressing modes used can be summarized below. Other addressing modes can be found in the Z80 CPU technical manual.

- (1) Register Addressing

- Example: In the instruction ADC A,B, ADC is the opcode which represents what kind of operation will be performed. The character A in the right means that the data will be added to A. The character B at the far right means that the data to be added to A is taken from register B.

- (2) Register Indirect Addressing

- A 16-bit register is used to store the memory address. Example: In the instruction SBC A,(HL), (HL) does not mean that HL will be subtracted from register A. Instead, the CPU takes the 16-bit data contained in HL as the memory address and then accesses the 8-bit data stored in this memory address. The 8-bit data pointed to by HL is finally subtracted from register A. IX and IY are called index registers. When a memory address is pointed to by IX or IY, an 8-bit byte which is less than +127 but larger than -128 can be added to this register.

For instance, the following two instructions can be used to add the data stored in the memory address pointed to by IX to the 8-bit data stored in the memory address pointed to by IX+2. The result is stored in register A.

| LD  | A,(IX)   |

|-----|----------|

| ADD | A,(IX+2) |

#### (3) Immediate Addressing

Example : OR OFH. On the right-hand side of the opcode OR, a hexadecimal number, OFH, is given. It means that the number OFH is logically ORed with the contents of register A. Therefore, the data is part of the instruction which is stored in memory. The CPU fetches the data by using the program counter (PC) as a reference address. The following instructions are examples of immediate addressing.

| LD  | В,8     |

|-----|---------|

| ADD | A,44H   |

| SUB | A, OA4H |

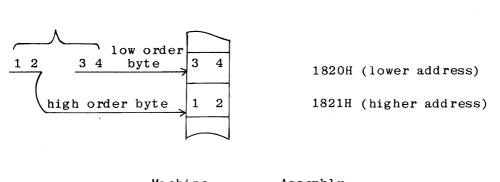

#### 3. Status Flags

After a logical or arithmetic operation is finished, the result will be stored in register A and some of the status flags (Carry, Overflow, Change Sign, Zero Result, Parity) will also be affected. These status flags will be stored in the flip flops in the Z-80 CPU. These flip flops form a register called the Flag Register. The data in this register can be moved to memory, like data in other registers, by specific instructions (PUSH instruction). Some of the status flags are given below.

#### (1) Carry Flag

This flag is the carry from highest order bit of the Accumulator. The carry flag will be set in either a signed or unsigned addition where the result is larger than an 8-bit munber. This flag is also set if a borrow is generated during a subtraction instruction. The carry flag can be used as a condition for jump, call, or return instructions. The carry flag also serves as an important linkage in multi-byte arithmetic operations. Three 8-bit data can be connected as a 24-bit data by using carry flag and four 8-bit data can be connected as a 32-bit data.

#### (2) Overflow/Parity Flag

When signed two's complement arithmetic operations are performed, this flag represents overflow. The Z-80 overflow flag indicates that the signed two's complement number in the accumulator has exceeded the maximum possible (+127) or is less than minimum possible (-128).

When an arithmetic operation is performed in the Z80-CPU, the number in register A can be assumed to be unsigned data (0 - 255) or signed data (-128 - +127). Thus, either the carry flag or the overflow flag can be affected by the arithmetic operation. The programmer decides which interpretation is desired. The following arithmetic operations are described on the right-hand side.

| 10101100      | <- | unsigned              | number | $\begin{array}{c} 172 \\ 232 \end{array}$ | or | signed | number  | -84  |

|---------------|----|-----------------------|--------|-------------------------------------------|----|--------|---------|------|

| +) 11101000   | <- | unsigned              | number |                                           | or | signed | number  | -24  |

| 1 <- 10010100 |    | unsigned<br>number -1 |        |                                           |    |        | y or si | gned |

| 01001010<br>+) 01000010 | <pre>&lt;- signed or unsigned number 74 &lt;- signed or unsigned number 66</pre> |

|-------------------------|----------------------------------------------------------------------------------|

|                         |                                                                                  |

| 0 <- 10001100           | <- unsigned number 140 but no carry, o                                           |

<- unsigned number 140 but no carry, or signed number -116 but overflow has occurred and the result becomes negative

change sign

For logical operations in the Z80-CPU, this flag is set if the parity of the 8-bit result in the accumulator is even. This flag is very useful in checking for parity errors occurring during data transmission. Since carry and overflow will never occur in logical operations, the parity and overflow status can be stored in the same flip flop. This flip flop is called the P/V flag. By testing this flip flop the programmer can check overflow after arithmetic operations and check parity after logical operations.

(3) Zero Flag

If register A is zero after a logical or arithmetic operation, this status will be registered in a flip flop called zero flag. The zero flag can be used as a condition for branch instructions. It is very useful in program looping.

(4) Sign Flag

If the leftmost bit (bit 7) of register A is 1 after a logical or arithmetic operation, the number in register A is interpreted as a negative number. The sign flag is then set to 1. This flag will be ignored if the programmer has assigned the data as unsigned numbers.

(5) The other flags designed for BCD arithmetic are not important for the programmer. The bit positions of the flags discussed above are shown below:

In microcomputers, it is usual to represent the contents of the flag register by two hexadecimal digits. The reader reader has to express this two-digit data with an 8-bit binary number. By referring to the bit positions in the flag register, the reader can obtain the status of the flag. For instance, if the flag register is 3CH, then the sign is positive, the value is non-zero, the parity is even or there is overflow has occurred but there is no carry. To know which flags will be affected by an instruction, the reader has to refer to the assembly language manual. Not all instructions will affect the status flags.

#### II. Example of Experiments

1. The following program can be used to add the contents of register D and register E together. The result will be stored in the pair register HL. Load the program into MPF-I and then execute it. Record the result.

| ORG | 1800H | ; Starting Address <- 1800H    |

|-----|-------|--------------------------------|

| LD  | A,E   | ; A <- E                       |

| ADD | A, D  | ; A <- A + D                   |

| LD  | L,A   | ; L <- A                       |

| LD  | Α,Ο   | ; A <- 0                       |

| ADC | A, 0  | ; $A \leftarrow A + 0 + Carry$ |

| LD  | H, A  | ; H <- A                       |

| RST | 38H   | ; Return to Monitor            |

| Preset | t Value Result of Program Execution |          |      |      |     |       |

|--------|-------------------------------------|----------|------|------|-----|-------|

| Regi   | ster                                | Register |      | Flag |     |       |

| D      | Е                                   | HL       | Sign | Zero | P/V | Carry |

| 5AH    | A6H                                 |          |      |      |     |       |

| 46H    | 77H                                 |          |      |      |     |       |

2. The following program can be used to add the 16-bit data in memory addresses 1A00H - 1A01H to the 16-bit value in the register pair DE. The result will be stored in the register pair HL. Load the program into MPF-I and execute it. Discuss the result obtained. preset values of memory: (1A01H) = \_\_\_\_\_,(1A00H) = \_\_\_\_\_,(1A00H) = \_\_\_\_\_,

| ORG<br>LD<br>ADD | A,(1A00H) | ; Starting address <- 1800H<br>; A <- (1A00H)<br>; A <- A + E |

|------------------|-----------|---------------------------------------------------------------|

| LD               | L,A       | ; L <- A                                                      |

| LD               | A,(1A01H) | ; A <- (1A01H)                                                |

| ADC              | A,D       | $A \leftarrow A + D + Carry$                                  |

| LD               | H, A      | ; H <- A                                                      |

| RST              | 38H       | , Return to monitor.                                          |

Result:

result

| HL       | = ,   |  |

|----------|-------|--|

| Carry    |       |  |

| Zero     |       |  |

| Overflow |       |  |

| Sign     | =     |  |

|          | · · · |  |

- 3. Revise the above program for a subtraction operation.

- 4. The following program can be used to add the 32-bit data in memory addresses 1A00H - 1A03H to the 32-bit data in memory addresses 1A04H - 1A07H. The result will be stored in memory addresses 1A08H - 1A0BH. The higher-order byte is stored in a higher address (This is conventional in microcomputer programming)

preset memory contents: ( 1A03H - 1A00H ) = \_\_\_\_\_ ( 1A07H - 1A04H ) = \_\_\_\_\_

| ORG | 1800H                                                  |

|-----|--------------------------------------------------------|

| LD  | В,4                                                    |

| LD  | IX,1AOOH                                               |

| AND | Α                                                      |

| LD  | A,(IX)                                                 |

| ADC | A,(IX+4)                                               |

| LD  | (IX+8),A                                               |

| INC | IX                                                     |

| DEC | В                                                      |

| JP  | NZ,LOOP                                                |

| RST | 38H                                                    |

|     | LD<br>LD<br>AND<br>LD<br>ADC<br>LD<br>INC<br>DEC<br>JP |

Result of program testing: results of program execution: ( 1AOBH - 1AO8H ) = \_\_\_\_\_

Flag Register = \_\_\_

5. If the instruction ADC A,(IX+4) is replaced by SBC A, (IX+4), then the above program can be used for a subtraction operation. If the instruction DAA is inserted immediately after the ADC or SBC instruction, then the program becomes a program for decimal addition or subtraction. Load the revised program to MPF-I and test it.

## Experiment 3 Binary Addition and Subtraction

Purposes:

- 1. To understand how an addition or subtraction operation is performed on a microcomputer.

- 2. To familiarize the reader with software programming techniques.

Time Required: 4 hours

I. Theoretical Background:

1. In this experiment, we only discuss unsigned binary integer addition and subtraction. For a N-bit binary number, its range is  $\langle 0,2 -1 \rangle$ . For instance, if N = 8, the range is  $\langle 0,255 \rangle$ ; if N = 16, the range is  $\langle 0,65535 \rangle$ . If the range of the numbers are expressed by hexadecimal digits, the ranges are  $\langle 0,FFH \rangle$ and  $\langle 0,FFFFH \rangle$ , respectively. If the sum of an addition operation is larger than the maximum value that can be represented by N bits, then carry is generated and the carry flag is set. In the subtraction operation, if the subtrahend is more than the minuend, a borrow is generated and the carry flag is set in the high order byte. The set carry bit indicates an incorrect result.

Example 3-1:

Single byte addition and subtraction.

Addition: 7FH + ADH = 12CH

01111111 -> 7FH +) 10101101 -> ADH 100101100 -> 12CH Carry

```

Subtraction: 7FH - ADH

Subtraction: ADH - 7FH = 2EH

01111111

10101101

) 01111111

•) 10101101

111010010

000101110

Borrow

Borrow

The answer is incorrect

The answer is correct

CY = 1)

CY = 0)

(

(

```

Example 3-2

Three-byte addition and subtraction

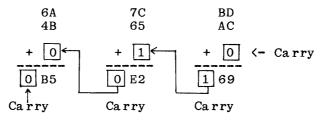

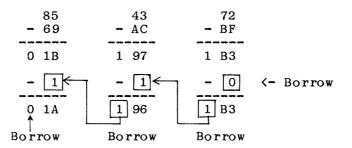

Addition: 6A7CBDH + 4B65ACH = B5E269H

Subtraction: 854372H - 69ACBFH =

The borrow of the highest-order byte is 0, thus the answer is correct. In multi-byte subtraction, the correctness of the result depends upon the borrow of the highest-order byte. If the borrow is 1, then the result is incorrect.

2. Order of data stored in memory:

The conventional way of storing multi-byte data in memory is: the lowest order byte is stored in the lowest address and the highest order byte is stored in the highest address. The address of the multi-byte data is usually expressed by its lowest address. For beginning atstance, the number 7325H is stored beginning at memory address A in the following way:

address A 25 <- low-order byte A + 1 73 <- high-order byte

If the starting address of 4 three-byte numbers stored in memory is A, the data and their addresses can be shown as follows :

| Address | A      | 56<br>7C                                         | 987C56H |

|---------|--------|--------------------------------------------------|---------|

|         | A + 3  | $\begin{array}{c}98\\43\\69\end{array}$          | AD6943H |

|         | A + 6  | $\begin{array}{c} AD \\ BC \\ 01 \end{array}$    | 2501BCH |

|         | A + 9  | 25<br>78<br>95                                   | 439578H |

|         | A + 12 | $\begin{array}{c} 33\\ 43\\ 21\\ 96 \end{array}$ | •••••   |

|         |        |                                                  |         |

3. Design of Addition/Subtraction Programs:

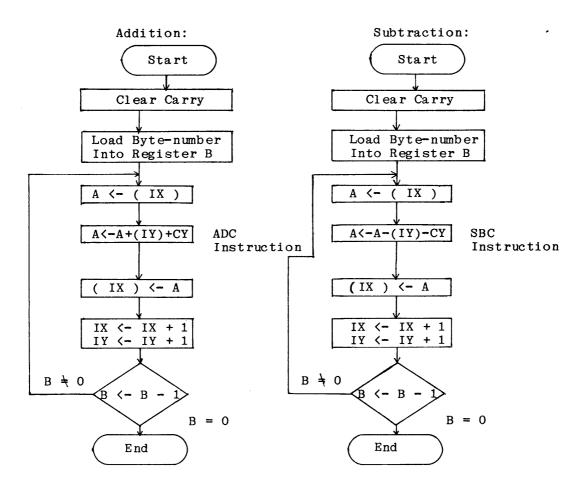

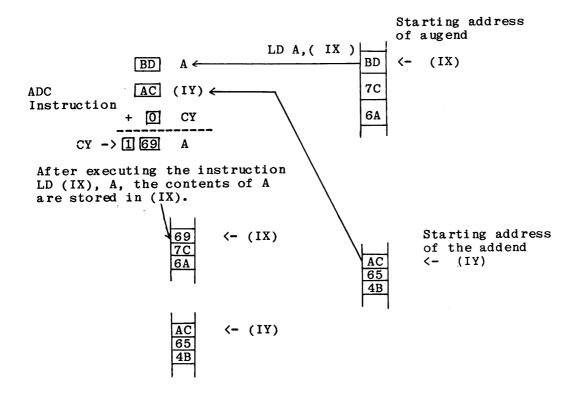

The data used in addition/subtraction operation are stored in memory according to the conventional method given above. The starting address of the augend/minuend is stored in index register IX. The starting address of addend/subtrahend is stored in index register IY. The byte-number of the data is stored in register B. First, clear CY and load the augend/ minuend into the accumulator. Then, use the indexed addressing mode instruction ADC ( SBC ) to proceed with the addition/ subtraction operation. The result is stored in the original Increment the index registers address of the augend/minuend. and compare register B with zero. Repeat the load augend, add, store increment cycle until the B register equals zero. Finally, test the carry flag to check if the result is correct. The only difference between the addition program and subtraction program is that the instruction ADC is used for addition operation and the instruction SBC is used for subtraction op-The flowcharts and programs are given below for comeration. parison:

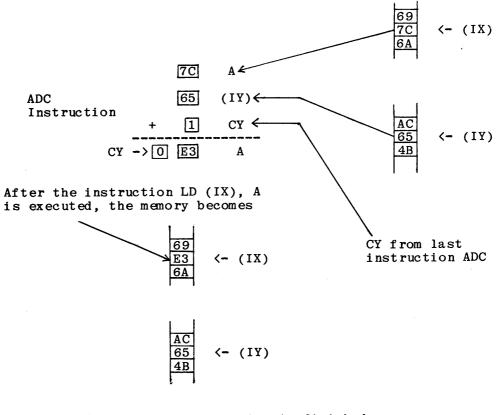

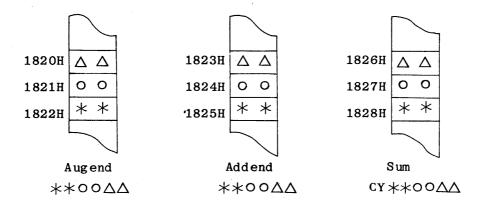

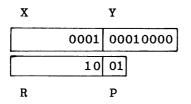

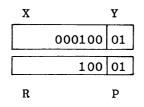

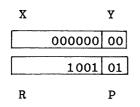

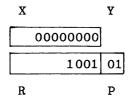

The following block diagram is given to demonstrate data transfer in an addition operation.

Instruction INC IX increases the value of IX by one. In the comment field the incrementation of IX can be shown as IX IX + 1 INC IY leads to IY <- IY + 1

In each of frames showing the results of an instruction step the current value pointed to by the index registers are indicated by

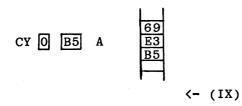

When B = 0, the program execution is finished and the memory becomes

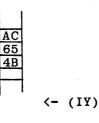

The addition program is given below. By replacing the instruction ADC A, (IY) by SBC A, (IY), the addition program becomes a subtraction program.

1. \*\*\* MPF-I EXAMPLE PROGRAM \*\*\* 2. 3-BYTE ADDITION ( UNSIGNED INTEGER ) 3. ENTRY ; AUGEND ADDRESS IN IX, 4. ADDEND ADDRESS IN IY. 5. EXIT : SUM IN AUGEND ADDRESS 6. 7. ADD3 : XOR A ; CLEAR CARRY FLAG 8. LD B, 3 ; BYTE NUMBER IN B 9. ADDLP : LD A, (IX) 10. ADC A, (IY) 11. LD (IX), A INC IX 12. INC IY 13. 14. DJNZ ADDLP 15. RET

4. Programming Technique:

From the above examples ( 3-1 and 3-2), we can see that the multibyte addition/subtraction operation can be accomplished by repeating the single-byte addition/subtraction operation, that is, by the loop operation of single-byte addition/subtraction. In the above program, register B is used as a loop counter. If the byte-number is 4, then 4 is loaded into B initially. Register B is decremented by 1 after each loop operation. The loop ends when B = 0. The instruction DJNZ is used for conditional jump. When B = 0, the program no longer executes the jump operation. Since ADC and SBC instructions are used in the programs, the CY is included in each addition/subtraction operation. Therefore, before the first byte addition/subtraction operation, the carry flag must be cleared (instruction XOR A). The index registers IX and IY are used as address pointers. By incrementing IX and IY, the CPU can access multibyte values stored in memory.

II. Student Exercises:

- 1. Load the above addition program into MPF-I and store it on magnetic tape.

- 2. Replace the last instruction RET in the program by RST 38H. Load the following data into memory. The starting addresses of augend and addend are assigned as 1900H and 1A00H, respectively.Execute the program and record the result in the following table.

| Augend          | Addend  | Answer | Check |

|-----------------|---------|--------|-------|

| <b>793865</b> H | ABCEDFH | CY =   |       |

| 009543H         | AB1236H | CY =   |       |

| 954717H         | 003390н | CY =   |       |

3. Replace the ADC instruction by the SBC instruction. Assign the starting addresses of minuend and subtrahend as 1900H and 1A00H, respectively. Execute the program and record the results obtained.

| Mi nuend | Subtrahend | Answer | Check |

|----------|------------|--------|-------|

| 683147H  | 336700Н    |        |       |

| 5935ABH  | 5877FFH    |        |       |

| 049677Н  | F65B79H    |        |       |

- 4. Express the data in the above two tables as five-byte data. Change the byte-counter to the proper value and execute the addition/subtraction program.

- 5. Write a program to add the 7-byte data in memory addresses 1A00H - 1A06H to the 7-byte data in memory addresses 1900H - 1906H and then subtract the 7-byte data in memory addresses 1940H - 1946H from the sum. The final result must be stored in memory with the starting address 1900H.

Experiment 3-1:

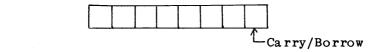

REG.F

The carry/borrow flag is used to indicate whether a carry/borrow is generated during an arithmetic or logical operation. If a carry/borrow is generated, then the flag is set to 1. Otherwise, the flag is zero. The carry flag is represented by bit 0 of the flag register.

In other words, the contents of the F register will be an even number if a carry/borrow is generated during the arithmetic or logical operation. If register F is an odd number, then no carry/borrow has been generated. Load the following program into MPF-I. Execute every instruction by using the Single Instruction method. Observe the variations of register F and record the results in the table.

\_28

| Address                                                                                                                                      | Machine<br>Language                                                                                                 |                                                                               | Assembl;<br>Languag                                                                              |                                       |                                                                             |                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|----------------------------------|

| 1800H<br>1801H<br>1803H<br>1805H<br>1807H<br>1809H<br>1809H<br>1800H<br>1800H<br>1810H<br>1812H<br>1812H<br>1814H<br>1816H<br>1818H<br>1818H | AF<br>3E7F<br>C6 AD<br>C6 23<br>D6 13<br>D6 B3<br>D6 15<br>AF<br>3E7F<br>CEAD<br>CE23<br>DE13<br>DE13<br>DE15<br>FF | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | SUB A,<br>SUB A,<br>SUB A,<br>XOR A<br>LD A, 7<br>ADC A,<br>ADC A,<br>SBC A,<br>SBC A,<br>SBC A, | ADH<br>23H<br>13H<br>B3H<br>15H<br>FH | $\begin{array}{ccc} CY, A & \langle & A \\ CY, A & \langle & A \end{array}$ | + 23H<br>- 13H<br>- B3H<br>- 15H |

| INSTRUCT                                                                                                                                     | ION                                                                                                                 | (3)                                                                           | (4)                                                                                              | (5)                                   | (6)                                                                         | (7)                              |

| BEFORE EX                                                                                                                                    | ECUT ION                                                                                                            | A<br>7 F                                                                      | A                                                                                                | A                                     |                                                                             | A                                |

| AFTER EXE                                                                                                                                    | ECUT ION                                                                                                            | + A D                                                                         | + 2 3                                                                                            | - 1 3                                 | - B 3                                                                       | - 1 5                            |

|                                                                                                                                              |                                                                                                                     |                                                                               |                                                                                                  |                                       |                                                                             |                                  |

|                                                                                                                                              |                                                                                                                     |                                                                               |                                                                                                  |                                       |                                                                             |                                  |

|                                                                                                                                              |                                                                                                                     |                                                                               |                                                                                                  | ,                                     |                                                                             |                                  |

|                                                                                                                                              |                                                                                                                     | (10)                                                                          | (11)                                                                                             | (12)                                  | (13)                                                                        | (14)                             |

|                                                                                                                                              | ·                                                                                                                   | CY                                                                            | CY                                                                                               | A                                     | A                                                                           | <b>A</b>                         |

|                                                                                                                                              |                                                                                                                     | A                                                                             | A                                                                                                | - 1 3                                 | - B 3                                                                       | - 1 5                            |

+ A D + 2 3 - CY - CY - CY

ШL СY

\_\_\_\_29

Experiment 3-2:

Referring to the operation for of 3-byte addition in example 3-3-2, write a basic addition program using only three kinds of instructions: XOR A, LD A,(nn) and ADD A,(nn). Assume that the memory addresses of the addend, augend and sum are assigned as follows:

Explanation: In the above example, we see the following rules of addition:

- (1) The addition operation moves from the low-order byte to the high-order byte, the carry generated in the low-order byte addition is added to the next higher order byte.

- (2) The addition operation is executed with the aid of the accumulator. Its result is also stored in the accumulator. Thus to add two bytes together, one byte must be loaded into the accumulator first (using the LD A,(nn) instruction). The other byte is then added to the accumulator (using the ADD A,(nn) instruction or the ADC A,(nn) instruction). The final result is stored in an assigned memory address (using the LD(nn),A instruction).

## **Experiment** 4

#### **Branch Instructions and Program Loops**

Purposes:

- 1. To familiarize the reader with the applications of conditional and unconditional branch instructions.

- 2. To familiarize the reader with the technique of designing program loops.

- 3. To practice using status flags in decision-making.

Time Required: 4 hours

#### I. Theoretical Background:

1. Program Counter:

The program counter (PC) is an important 16-bit register in the CPU. When the voltage level of the RESET pin (pin 26) of the CPU drops to 0 and then rises to 1 (by pressing the RS key), the PC will be cleared to 0000H. The program execution is then started from address 0000H according to the clock pulses supplied by the system hardware. Once the CPU has fetched one byte of each instruction from memory, the PC will be incremented by one automatically. (The internal control circuit in the CPU determines how many bytes are contained in the instruction after the CPU has fetched the first byte of the instruction. The instruction will be executed only when the PC has been incremented by the number of bytes in the instruction). Usually, the program is fetched from the memory instruction by the instruction for execution, starting from the low memory address.

2. Branch Instructions:

At any address, the PC can be changed to another address if the programmer doesn't want the program executio to continue sequentially (For instance, when there is no memory beyond that address or the program is not stored in that area). The program then jumps to another address and continue its execution. For example, the following assembly language means that the PC will be changed to 1828H after this instruction has been executed, and the program execution continues from address 1828H.

LD PC, 1828H (This instruction is illegal in Z80 assembly language)

Actually, in assembly language, JP (Jump) is used to indicate the change in sequence of program execution. The instruction has the same meaning as:

LD ·PC, 1828H JP 1828H

3. Conditional Branch Instructions:

A conditional branch instruction performs the jump operation if some specified conditions are met. These conditions are all dependent on the data in the flag register. This function makes the microcomputer capable of responding to various external conditions. It is also an indispensable tool for designing program loops. The actions of the following instructions are described in the comments to the right of the instruction:

| СР  | 10H |       | ; | Compare the accumulator with 10H and set the proper flag.                                                   |

|-----|-----|-------|---|-------------------------------------------------------------------------------------------------------------|

| JP  | Ζ,  | 1828H | ; | If the zero flag is set, i.e. A = 10H,<br>then jump to address 1828H and continue<br>the program execution. |

| JΡ  | C,  | 245AH | ; | If the carry flag is set, i.e. A < 10H,<br>then jump to 245AH to execute other<br>program.                  |

| ADD | А,В |       | ; | Otherwise, i.e. $A > 10$ , continue the program execution.                                                  |

The condition of a conditional branch instruction is written after JP:

| (1) JP C, XXXX  | ; If there is a carry, or carry flag = 1,<br>then jump to XXXX.                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------|

| (2) JP NC, XXXX | ; If there is no carry, or carry flag = 0<br>then jump to XXXX.                                                      |

| (3) JP Z, XXXX  | ; If zero flag = 1, or the result of previous operation is zero, then jump to XXXX.                                  |

| (4) JP NZ, XXXX | ; If zero flag = 0, then jump to $XXXX$ .                                                                            |

| (5) Jp PE, XXXX | ; If parity flag = 1 (even), or there was<br>an overflow in the previous arithmetic<br>operation, then jump to XXXX. |

| (6) JP PO, XXXX | ; If P/V flag = 0 (odd parity or no overflow)<br>then jump to XXXX.                                                  |

| (7) JP | P, XXXX ; | If sign flag = 0 (the sign of result of previo's operation is positive) then jump to XXXX. |

|--------|-----------|--------------------------------------------------------------------------------------------|

| (8) JP | M, XXXX ; | If sign flag = 1 (negative) then jump to XXXX.                                             |

### 4. Jump Relative:

To reduce the memory space occupied by the program and also reduce the cost of the microcomputer system, the Z80 microcomputer can use relative addresses to specify the displacement of a program jump. Since most displacements in a jump are within the rage between +127 and -128, a one byte number can be used to indicate this displacement. One byte of memory is saved for each jump operation compared with the two-byte absolute address in JP instructions. The operations of the following instructions are described in the commands to the right of the instruction. JR 10H ; Jump forward 10H (16) locations from the

- ; Jump forward 10H (16) locations from the present program counter (the address of the next instruction). Actually, the address of the next instruction to be executed is obtained by adding 10H to the present PC.

- JR C,FOH ; If carrry flag = 1, then jump backward 10H (16) locations from the present program counter. Since the leftmost bit of FOH is 1, it is recognized as a negative number (its 2's complement is 10H).

- JR NC,7FH ; If carry flag = 0, than jump forward 127 locations (maximum value)

- JR Z,80H ; If zero flag = 1, i.e. the result of the previous operation is zero, then jump backward 128 locations. 80H (-128) is the minimum negative number that can be used in a relative address.

From the above examples, we can see that a positive relative address means jumping forward. The largest displacement then is 7FH (+127). A negative relative address means jumping backward. Its largest displacement is 80H (-128). The displacement is always measured from the address of the next instruction's op code. Relative jumps can be unconditional or conditional. The conditional jump depends on the status of the carry or zero flag. In the Z80 system, the data in the sign or P/V flag cannot be used as the condition of a relative jump.

#### 5. Program Loop:

One of the important advantages of a computer is that it can repeat the steps in a repetitive task as many times as is

necessary to complete the task. This is accomplished by using a program loop. Looping is a very powerful tool in program design. A basic program loop must contain the following:

- (1) A loop's counter preset with the number of loops to be executed. Usually, a CPU register is used as a loop counter. Of course, memory can also be used as a counter.

- (2) The loop counter is decremented by 1 after one cycle of the loop has been executed. After each cycle the value of the loop counter must be checked. If the counter is not 0, then the loop repeats until the loop counter equals to 0.

The following program can be used to add the 8-bit data in memory addresses 1900H - 190FH and store the result in the DE register pair. This is a typical application of a program loop.

| LD C,10H    | ; | Use register C as the loop counter. Since<br>sixteen bytes data are to be added together,<br>10H is preset in C.                                                                       |

|-------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XOR A       | ; | Clear the accumulator                                                                                                                                                                  |

| LD HL,1900H | ; | Use the HL register pair as the address pointer.<br>The contents of the memory pointed to by HL<br>will be added to register A.<br>The first address is 1900H.                         |

| LD D,A      | ; | Register D is used to store the carry<br>generated during the addition operation.<br>Clear Register D.                                                                                 |

| ADD A,(HL)  | ; | Add the contents of the memory address pointed<br>to by HL to Register A. This instruction will<br>be repeated 16 times. XX is assigned<br>as the label of this instruction's address. |

| INC HL      | ; | Increment HL by 1. The new HL points to the<br>next byte in data memory to be added to<br>Register A.                                                                                  |

| JR NC,YY    | ; | If no carry is generated, jump to address<br>YY to continue program execution.                                                                                                         |

| INC D       | ; | If a carry is generated, add this carry to Register D.                                                                                                                                 |

| DEC C       | ; | Decrement register C by 1.                                                                                                                                                             |

| JR NZ,XX    | ; | If the result is not zero (zero flag = 0),<br>the program loop has not finished. Jump to<br>XX to repeat the loop.                                                                     |

XX

YY

LD E,A ; If zero flag = 1, then all data have been added together. Load A into E, the answer will be stored in the DE register pair.

END

There are various methods of designing a program loop. Try to design the program loops described in the following illustrations.

- II. Example Experiments:

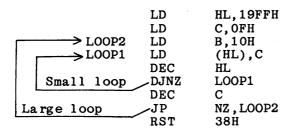

- 1. A program loop with a loop number of less than 256 : If the loop number is less than 256, register B is recommended as the loop counter. At the end of the loop, the DJNZ instruction can be used to decrement register B. If the result is not zero, jump to the assigned location using the relative jump method to continue the program execution. Try to analyze the following program and verify its function by loading it into the MPF-I and executing it.

|        | ORG   | 1800H    |

|--------|-------|----------|

|        | LD    | HL,1900H |

|        | LD    | B,20H    |

| _→LOOP | LD    | (HL),A   |

|        | INC   | HL       |

|        | —DJNZ | LOOP     |

|        | RST   | 38H      |

Experimental result:

- (1) Preset register A to 0 and then execute the above program Results: Contents of memory addresses 1900H - 191FH: Contents of memory address 1920H:

- (2) Preset register A to 55H and execute the above program. Results:

- (3) Preset register A to 64H and replace the second instruction LD B,20H by the instruction LD B,0. Execute the program again. Results: Contents of memory addresses 1900H - 19FFH:

Discussion:

2. Nested loops:

In a more complicated program, a loop can be totally nested or embedded inside another loop. The following program can be used to divide the 256 bytes of data stored in memory into 16 groups. The starting address of the memory is 1900H. Put the contents of each group of data in the form of a hexadecimal number: 0....(1st set), 1.....(2nd set), 2.....(3rd set),....,F..... (16th set).

- (1) Translate the above program into machine language and then load it into the MPF-I. Execute the program. Result :

- (2) Revise the above program such that the 16 bytes of the first group are all "F", and the 16 bytes of the last group are all "0".

- 3. A program loop with loop number larger than 256: If the loop number is larger than 256, a 16-bit register can be used as the loop counter. But, in the Z80 system, incrementing or decrementing a 16-bit register can not affect the status flag. Thus, some auxiliary instruction is used to determine whether the loop counter is zero. The following program is supposed to be able to set all data in RAM 1880H - 19FFH to AAH. Try to find the errors in this program and correct them. Load the correct program into the MPF-I and record the result of the program execution.

|      | ORG           | 1800H     |

|------|---------------|-----------|

|      | LD            | BC,0180H  |

|      | LD            | HL,1880H  |

| LOOP | LD            | (HL),QAAH |

|      | INC           | HL        |

|      | DEC           | BC        |

|      | $\mathbf{JR}$ | NZ,LOOP   |

|      | HALT          |           |

4. A program loop without a down counter : A program loop need not use a down counter. The function of the down counter can be replaced by using an up counter or using the method of address comparision or data comparison. Study the method used in the following program loops. Load the programs into MPF-I and execute them.

(1) Move the data string in the memory (RAM) section with starting address 1B00H to the memory (RAM) section with starting address 1A00H. The movement will be terminated when data OFFH is found.

|      | ORG | 1800H     |

|------|-----|-----------|

|      | LD  | HL,1BOOH  |

|      | LD  | DE, 1AOOH |

| LOOP | LD  | A,(HL)    |

|      | LD  | (DE),A    |

|      | CP  | OFFH      |

|      | JR  | Z,EXIT    |

|      | INC | HL        |

|      | INC | DE        |

|      | JR  | LOOP      |

| EXIT | RST | 38H       |

|      |     |           |

(2) Replace all the data stored in the memory section starting from the address pointed to by HL to the address pointed to by DE with their corresponding 2's complement. In testing the program, the values of HL and DE must be preset first. The value of HL must be larger than that of DE.

|      | ORG | 1800H   |

|------|-----|---------|

| LOOP | LD  | A,(HL)  |

|      | NEG |         |

|      | LD  | (HL),A  |

|      | INC | HL      |

|      | AND | А       |

|      | SBC | HL,DE   |

|      | ADD | HL,DE   |

|      | JR  | NZ,LOOP |

# Experiment 5 Stack and Subroutines

Purposes:

- 1. To understand the meaning and applications of stack

- 2. To understand the designing techniques and applications of subroutines.

Time Required: 4 hours

- I. Theoretical Background

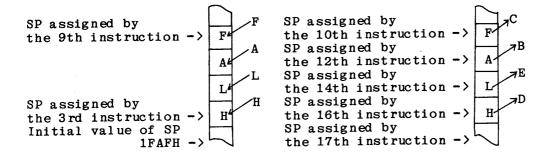

- 1. Stack: In program design, a stack is recognized as a memory section which has only one port for input and output. Data are written in or retreived from stack via this port. The first item of data placed in stack is said to be at the bottom of stack. The data most recently placed in stack is said to be at the top of stack. Thus, a stack is also called a last-in first-out memory. A stack can be constructed by hardware shift registers or general RAMs. In the Z80 microcomputer system, the programmer can assign a region of RAM as the stack. To define a stack at the top of RAM, the highest address of RAM is incremented by 1 and then loaded into the stack pointer (SP) in the CPU. The following program and diagrams illustrate the operation of stack.

| Instruction<br>Number | Instruction          | Comment                                                                                                                    |

|-----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|

|                       | LD SP,1FAFH          | ; Stack pointer is set to 1FAFH, i.e. the<br>RAM section with address less than or<br>equal to 1FAEH is assigned as stack. |

| (2)                   | DEC SP               | ; Decrement SP by 1. Stack pointer is at 1FAEH, i.e. at the bottom of stack.                                               |

| (3)                   | LD (SP),H            | ; Load the contents of register H into memory (RAM) address 1FAEH.                                                         |

|                       | DEC SP<br>LD (SP), L | ; Decrement SP by 1 again.<br>; Place the contents of L at the top of stack (i.e. above H).                                |

| (6)<br>(7)            | DEC SP<br>LD (SP),A  | ; Place the contents of A at the top of stack (i.e. above L).                                                              |

| (8)                   | DEC SP               |                                                                                                                            |

| (9)  | LD (SP), F | ; | Place the contents of F at the top of stack (i.e. above A). |

|------|------------|---|-------------------------------------------------------------|

|      | •          |   |                                                             |

|      | • •        |   |                                                             |

|      | •          |   |                                                             |

|      | •          |   |                                                             |

| (10) | LD C, (SP) | ; | Pop one byte of data from the top                           |

| • •  |            |   | of stack and move it to register C.                         |

| (11) | INC SP     | ; | Increment SP by 1. SP is moved towards                      |

| (11) |            |   | the top of the stack.                                       |

| (12) | LD B,(SP)  | ; | Pop data from the top of stack.                             |

| (13) | INC SP     | ; | Increment SP by 1 again.                                    |

| (14) |            | ; | Pop data from the top of stack and                          |

| (/   |            | • | move it to register E.                                      |

| (15) | INC SP     |   | -                                                           |

| (16) |            | : | Pop data from the top of stack and                          |

| (±0) |            |   | move it to register D. This data is the                     |

|      |            |   | first one that is stored in stack.                          |

| (17) | INC SP     | : | SP is at the initial value.                                 |

| (1)  |            | , |                                                             |

RAM

RAM

Push data onto the stack

Pop data from the stack

From the above illustrations of stack operation, we can see that data can be stored in RAM by using SP as the pointer. SP is decremented by 1 whenever one-byte of data is stored in and the stack area becomes larger. The SP will be incremented by 1 whenever one-byte data is retrieved from the stack area and the stack area becomes smaller. The process of decrementing SP (pushing data onto stack) or incrementing SP (popping data out of stack) can be accomplished automatically by special hardware design. A stack can

.39

also be used to store a 16-bit address (or data). In the Z80/8085 system, there are instructions to push a 16-bit register pair onto stack and pop a 16-bit data out of stack. During each operation, SP is decremented or incremented by 2. The following program is equivalent in function to that of the program given above.

| LD SP, | 1FAFH | ; | Same | as | 1st | instruction.                   |

|--------|-------|---|------|----|-----|--------------------------------|

| PUSH   | HL    |   |      |    |     | (2)(3)(4)(5) instructions.     |

| PUSH   | AF    |   |      |    |     | (6)(7)(8)(9) instructions.     |

| POP    | BC    | : | Same | as | no. | (10)(11)(12)(13) instructions. |

| POP    | DE    | ÷ | Same | as | no. | (14)(15)(16)(17) instructions. |

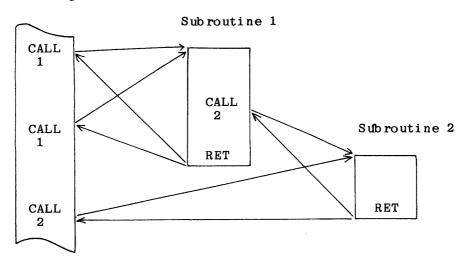

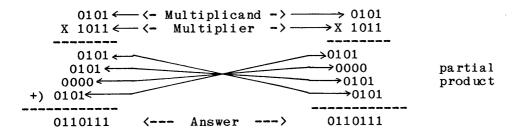

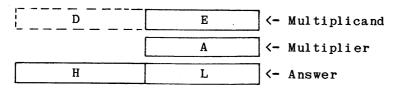

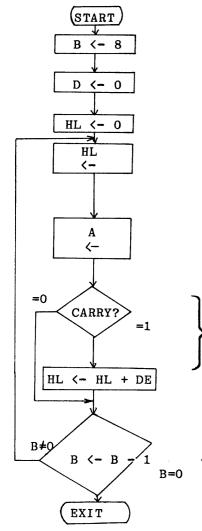

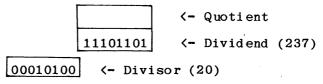

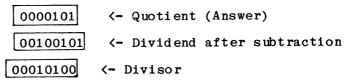

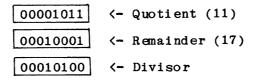

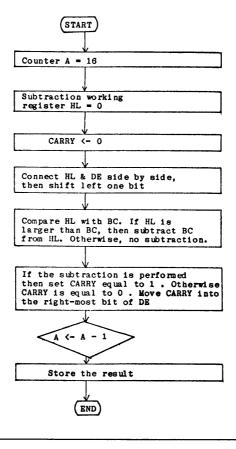

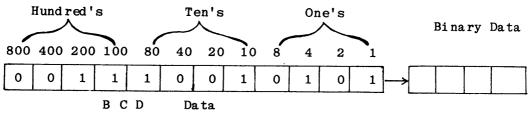

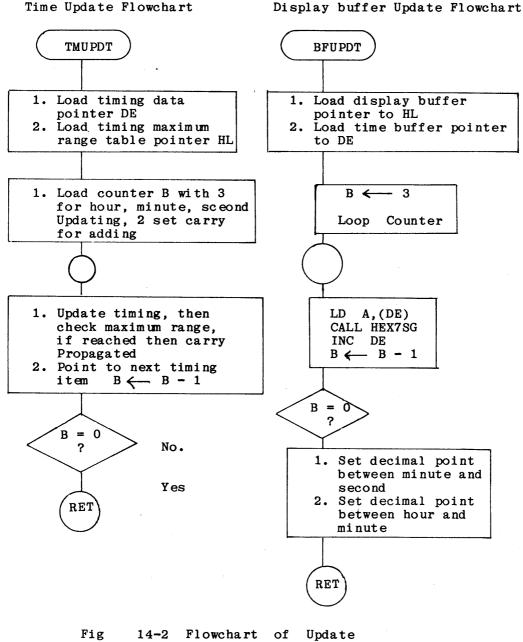

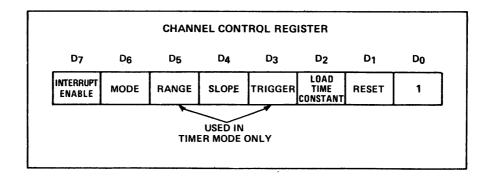

Instructions PUSH and POP can be used to temporarily store data in registers and also used to transfer register data. An example is given below.